1

GATE ECE 2023

MCQ (Single Correct Answer)

+1

-0.33

The synchronous sequential circuit shown below works at a clock frequency of 1 GHz. The throughput, in Mbits/s, and the latency, in ns, respectively, are

2

GATE ECE 2018

Numerical

+1

-0

A traffic signal cycles from GREEN to YELLOW, YELLOW to RED and RED to GREEN.

In each cycle, GREEN is turned on for 70 seconds, YELLOW is turned on for

5 seconds and the RED is turned on for 75 seconds. This traffic light has to be implemented

using a finite state machine (FSM). The only input to this FSM is a clock of 5 second period.

The minimum number of flip-flops required to implement this FSM is _______.

Your input ____

3

GATE ECE 2017 Set 1

Numerical

+1

-0

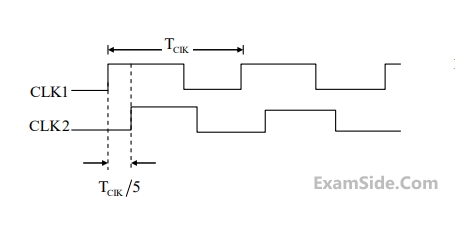

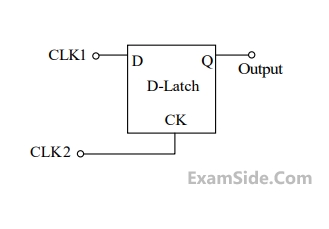

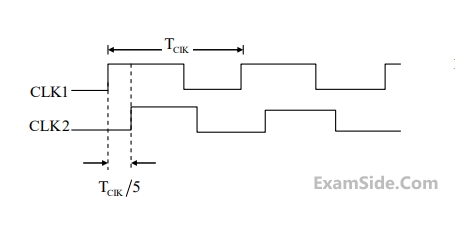

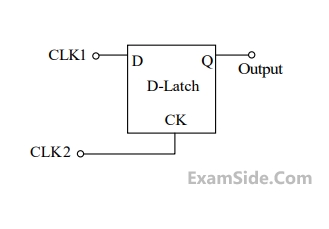

Consider the D-Latch shown in the figure, which is transparent when its clock input CK is high and has zero propagation delay. In the figure, the clock signal CLK1 has a 50% duty cycle and CLK2 is a one-fifth period delayed version of CLK1. The duty cycle at the output latch in percentage is ___________.

Your input ____

4

GATE ECE 2017 Set 1

MCQ (Single Correct Answer)

+1

-0.3

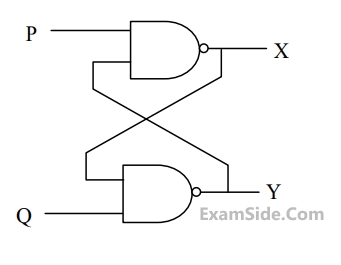

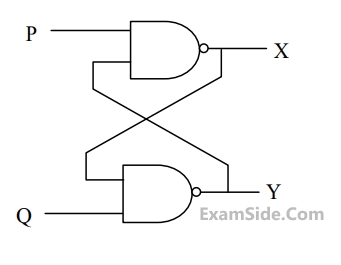

In the latch circuit shown, the NAND gates have non-zero, but unequal propagation delays. The present input condition is: P = Q = "0‟. If the input condition is changed simultaneously to P = Q = "1", the outputs X and Y are

Questions Asked from Sequential Circuits (Marks 1)

Number in Brackets after Paper Indicates No. of Questions

GATE ECE 2023 (1)

GATE ECE 2018 (1)

GATE ECE 2017 Set 1 (2)

GATE ECE 2016 Set 2 (1)

GATE ECE 2015 Set 2 (1)

GATE ECE 2015 Set 3 (1)

GATE ECE 2014 Set 1 (1)

GATE ECE 2014 Set 3 (2)

GATE ECE 2012 (1)

GATE ECE 2011 (1)

GATE ECE 2010 (1)

GATE ECE 2005 (2)

GATE ECE 2004 (2)

GATE ECE 2003 (1)

GATE ECE 1998 (1)

GATE ECE 1997 (1)

GATE ECE 1995 (2)

GATE ECE 1994 (1)

GATE ECE 1993 (1)

GATE ECE 1992 (1)

GATE ECE 1991 (1)

GATE ECE 1990 (1)

GATE ECE 1988 (1)

GATE ECE 1987 (2)

GATE ECE Subjects

Signals and Systems

Representation of Continuous Time Signal Fourier Series Discrete Time Signal Fourier Series Fourier Transform Discrete Time Signal Z Transform Continuous Time Linear Invariant System Transmission of Signal Through Continuous Time LTI Systems Discrete Time Linear Time Invariant Systems Sampling Continuous Time Signal Laplace Transform Discrete Fourier Transform and Fast Fourier Transform Transmission of Signal Through Discrete Time Lti Systems Miscellaneous Fourier Transform

Network Theory

Control Systems

Digital Circuits

General Aptitude

Electronic Devices and VLSI

Analog Circuits

Engineering Mathematics

Microprocessors

Communications

Electromagnetics