Marks 1

1

In a DRAM,

GATE ECE 2017 Set 2

2

A 16 Kb (=16,384 bit) memory array is designed as a square with an aspect ratio of one (number of rows is equal to the number

of columns). The minimum number of address lines needed for the row decoder is _______.

GATE ECE 2015 Set 1

3

Each cell of a static Random Access Memory Contains

GATE ECE 1996

4

The minimum number of MOS transistors required to make a dynamic RAM cell is

GATE ECE 1995

5

A PLA can be used

GATE ECE 1994

6

A dynamic RAM consists of

GATE ECE 1994

7

Choose the correct satatement(s) from the following:

GATE ECE 1992

Marks 2

1

A 2 $$ \times $$ 2 ROM array is built with the help of diodes as shown in the circuit below. Here W0

and W1 are signals that select the word lines and B0 and B1 are signals that are output of the

sense amps based on the stored data corresponding to the bit lines during the read operation.

During the read operation, the selected word line goes high and the other word line is in a high impedance state. As per the implementation shown in the circuit diagram above, what are the bits corresponding to Dij (where i = 0 or 1 and j = 0 or 1) stored in the ROM?

During the read operation, the selected word line goes high and the other word line is in a high impedance state. As per the implementation shown in the circuit diagram above, what are the bits corresponding to Dij (where i = 0 or 1 and j = 0 or 1) stored in the ROM?

GATE ECE 2018

2

If WL is the Word Line and BL the Bit Line, an SRAM cell is shown in

GATE ECE 2014 Set 3

3

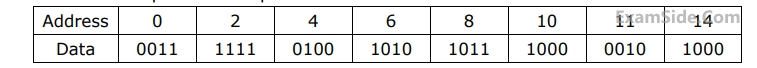

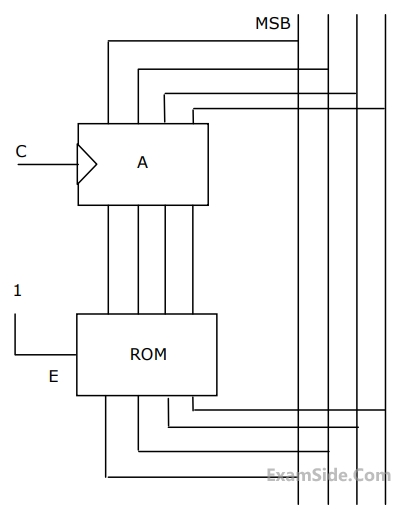

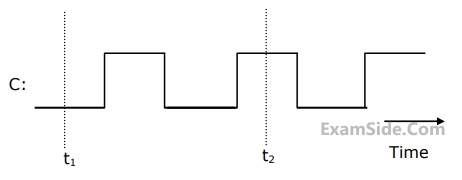

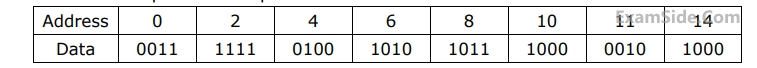

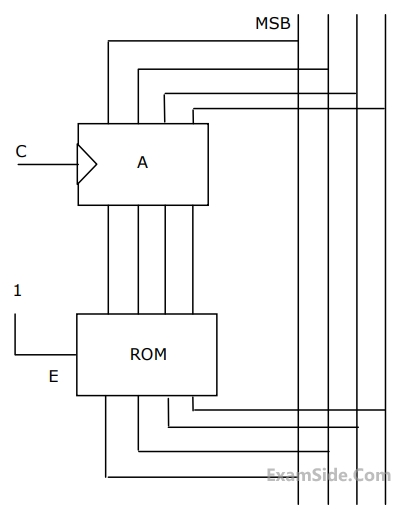

In the circuit shown in Figure, A is a parallel in, parallel-out 4-bit register, which loads at the rising edge of the clock C. The input lines are connected to a 4-bit bus, W. Its output acts as the input to a 16×4 ROM whose output is floating when

the enable input E is 0. A partial table of the contents of the ROM is as follows

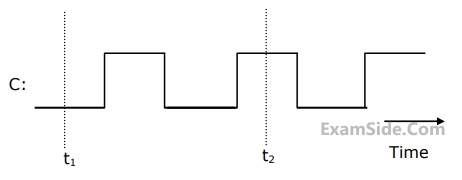

The clock to the register is shown, and the data on the W bus at time t$$_1$$ is 0110. The data on the bus at time t$$_2$$ is

GATE ECE 2003

4

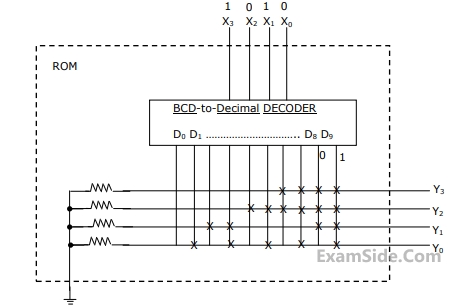

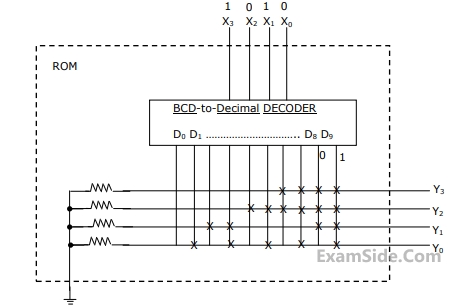

If the input X$$_3$$, X$$_2$$, X$$_1$$, X$$_0$$ to the ROM in figure 2.12 are 8-4-2-1 BCD numbers, then the outpus are Y$$_3$$,Y$$_2$$, Y$$_1$$, Y$$_0$$ are

GATE ECE 2002