1

GATE ECE 2011

MCQ (Single Correct Answer)

+2

-0.6

Two D flip-flops are connected as a synchronous counter that goes through the following QB QA sequence $$00 \to 11 \to 01 \to 10 \to 00 \to ......$$

2

GATE ECE 2009

MCQ (Single Correct Answer)

+2

-0.6

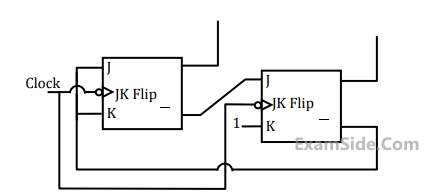

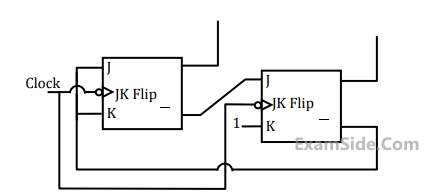

What are the counting states (Q1, Q2) for the counter shown in the figure below?

3

GATE ECE 2008

MCQ (Single Correct Answer)

+2

-0.6

For each of the positive edge-triggered J-K flip flop used in the following future, the propagation delay is $$\Delta $$T

Which of the following waveforms correctly represents the output at Q1?

4

GATE ECE 2007

MCQ (Single Correct Answer)

+2

-0.6

For the circuit shown, the counter state (Q1 Q0) follows the sequence

Questions Asked from Sequential Circuits (Marks 2)

Number in Brackets after Paper Indicates No. of Questions

GATE ECE 2025 (2)

GATE ECE 2024 (1)

GATE ECE 2023 (1)

GATE ECE 2022 (2)

GATE ECE 2018 (1)

GATE ECE 2017 Set 1 (2)

GATE ECE 2017 Set 2 (1)

GATE ECE 2016 Set 2 (2)

GATE ECE 2015 Set 2 (1)

GATE ECE 2015 Set 3 (2)

GATE ECE 2014 Set 2 (2)

GATE ECE 2014 Set 1 (1)

GATE ECE 2012 (1)

GATE ECE 2011 (2)

GATE ECE 2009 (1)

GATE ECE 2008 (1)

GATE ECE 2007 (2)

GATE ECE 2006 (1)

GATE ECE 2004 (1)

GATE ECE 2003 (1)

GATE ECE 2001 (1)

GATE ECE 2000 (2)

GATE ECE 1999 (1)

GATE ECE 1998 (1)

GATE ECE Subjects

Signals and Systems

Representation of Continuous Time Signal Fourier Series Discrete Time Signal Fourier Series Fourier Transform Discrete Time Signal Z Transform Continuous Time Linear Invariant System Transmission of Signal Through Continuous Time LTI Systems Discrete Time Linear Time Invariant Systems Sampling Continuous Time Signal Laplace Transform Discrete Fourier Transform and Fast Fourier Transform Transmission of Signal Through Discrete Time Lti Systems Miscellaneous Fourier Transform

Network Theory

Control Systems

Digital Circuits

General Aptitude

Electronic Devices and VLSI

Analog Circuits

Engineering Mathematics

Microprocessors

Communications

Electromagnetics