1

GATE ECE 2017 Set 2

Numerical

+2

-0

A MOS capacitor is fabricated on p-type Si (silicon) where the metal work function is 4.1 eV

and electron affinity of Si is 4.0 eV, Ec - EF = 0.9 eV; where Ec and EF are conduction band minimum and the Fermi energy levels of Si, respectively. Oxide$${\varepsilon _r} = \,\,3.9,\,\,\,{\varepsilon _{0\,\,}}=\,8.85 \times {10^{ - 14}}$$ F/cm, oxide thickness $${t_{ox}} = 0.1\,\mu m$$

and electronic charge q = $$1.6 \times {10^{ - 19}}$$ C. If the measured flat band

voltage of the capacitor is –1V, then the magnitude of the fixed charge at the oxide semiconductor

interface, in nC/cm2, is __________.

Your input ____

2

GATE ECE 2017 Set 1

Numerical

+2

-0

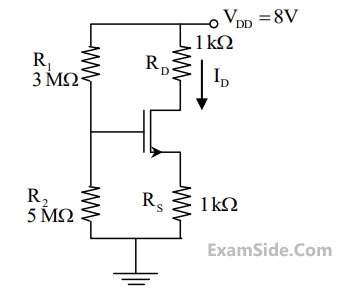

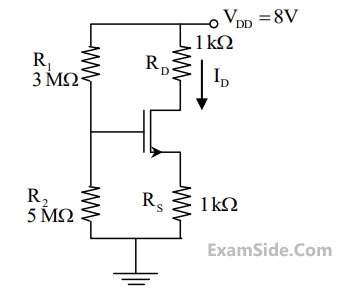

For the circuit shown, assume that the NMOS transistor is in saturation. Its threshold voltage

Vtn = 1 V and its trans-conductance parameter $${\mu _n}{C_{ox}}\left( {{W \over L}} \right) = 1m{\rm A}/{V^2}.$$ Neglect channel length modulation and body bias effects. Under these conditions the drain current ID in mA is______.

Your input ____

3

GATE ECE 2016 Set 3

Numerical

+2

-0

Figures $${\rm I}$$ and $${\rm I}{\rm I}$$ show two MOS capacitor of unit area. The capacitor in Figure I has insulator materials X (of thickness t1 = 1 nm and dielectric constant $${\varepsilon _1}$$ = 4) and Y (of thickness t2 =3 nm and dielectric constant $${\varepsilon _2}$$ = 200). The capacitor in Figure $${\rm I}{\rm I}$$ has only insulator material X of thickness teq. If the capacitors are of equal capacitance, then the value of teq (in nm) is ______

Your input ____

4

GATE ECE 2016 Set 3

Numerical

+2

-0

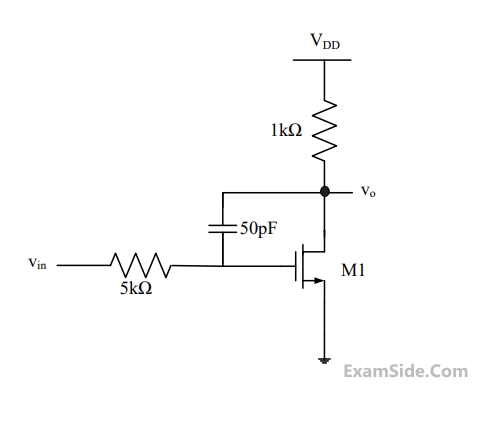

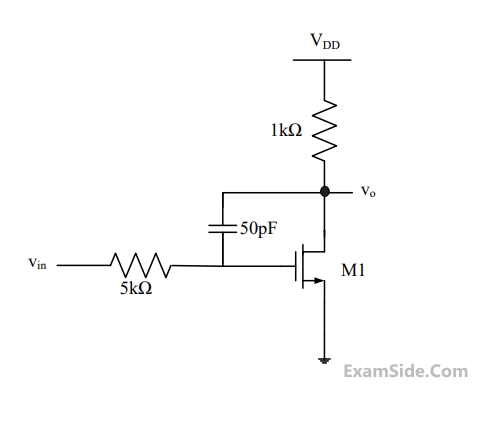

In the circuit shown in the figure, transistor M1 is in saturation and has transconductance

gm = 0.01 siemens. Ignoring internal parasitic capacitances and assuming the channel length

modulation $$\lambda $$ to be zero, the small signal input pole frequency (in kHz) is _____

Your input ____

Questions Asked from IC Basics and MOSFET (Marks 2)

Number in Brackets after Paper Indicates No. of Questions

GATE ECE 2024 (1)

GATE ECE 2023 (1)

GATE ECE 2017 Set 2 (3)

GATE ECE 2017 Set 1 (1)

GATE ECE 2016 Set 3 (3)

GATE ECE 2016 Set 2 (2)

GATE ECE 2016 Set 1 (1)

GATE ECE 2015 Set 2 (1)

GATE ECE 2015 Set 3 (2)

GATE ECE 2015 Set 1 (2)

GATE ECE 2014 Set 1 (1)

GATE ECE 2014 Set 3 (3)

GATE ECE 2014 Set 2 (2)

GATE ECE 2013 (1)

GATE ECE 2012 (4)

GATE ECE 2009 (2)

GATE ECE 2008 (3)

GATE ECE 2007 (1)

GATE ECE 2006 (1)

GATE ECE 2004 (1)

GATE ECE 2003 (3)

GATE ECE Subjects

Network Theory

Control Systems

Electronic Devices and VLSI

Analog Circuits

Digital Circuits

Microprocessors

Signals and Systems

Representation of Continuous Time Signal Fourier Series Discrete Time Signal Fourier Series Fourier Transform Discrete Time Signal Z Transform Continuous Time Linear Invariant System Transmission of Signal Through Continuous Time LTI Systems Discrete Time Linear Time Invariant Systems Sampling Continuous Time Signal Laplace Transform Discrete Fourier Transform and Fast Fourier Transform Transmission of Signal Through Discrete Time Lti Systems Miscellaneous Fourier Transform

Communications

Electromagnetics

General Aptitude