1

GATE ECE 1998

MCQ (Single Correct Answer)

+1

-0.3

The noise margin of a TTL gate is about

2

GATE ECE 1998

MCQ (Single Correct Answer)

+1

-0.3

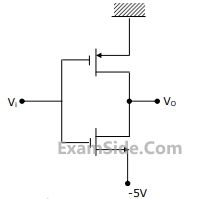

The threshold voltage for each transistor in Fig.2.5, is 2V. For this circuit to work as an inverter, Vi must take the values

3

GATE ECE 1997

MCQ (Single Correct Answer)

+1

-0.3

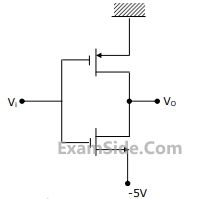

For the NMOS logic gate shown in figure, the logic function implemented is

4

GATE ECE 1997

MCQ (Single Correct Answer)

+1

-0.3

The gate delay of an NMOS inverter is dominated by charge time rather than discharge time because

Questions Asked from Logic Families (Marks 1)

Number in Brackets after Paper Indicates No. of Questions

GATE ECE Subjects

Signals and Systems

Representation of Continuous Time Signal Fourier Series Fourier Transform Continuous Time Signal Laplace Transform Discrete Time Signal Fourier Series Fourier Transform Discrete Fourier Transform and Fast Fourier Transform Discrete Time Signal Z Transform Continuous Time Linear Invariant System Discrete Time Linear Time Invariant Systems Transmission of Signal Through Continuous Time LTI Systems Sampling Transmission of Signal Through Discrete Time Lti Systems Miscellaneous

Network Theory

Control Systems

Digital Circuits

General Aptitude

Electronic Devices and VLSI

Analog Circuits

Engineering Mathematics

Microprocessors

Communications

Electromagnetics