1

GATE ECE 2009

MCQ (Single Correct Answer)

+2

-0.6

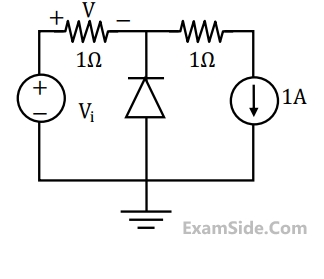

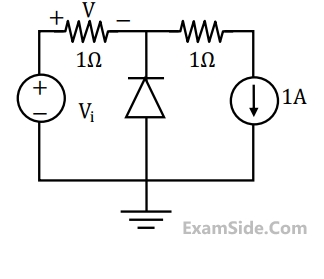

In the circuit below, the diode is ideal. The voltage V is given by

2

GATE ECE 2007

MCQ (Single Correct Answer)

+2

-0.6

A P+-N junction has a built-in potential of 0.8 V. The depletion layer width at a

reverse bias of 1.2V is 2 µm. For a reverse bias of 7.2 V, the depletion layer

width will be:

3

GATE ECE 2005

MCQ (Single Correct Answer)

+2

-0.6

The Zener diode in the regulator circuit shown in figure has a Zener voltage of

5.8 Volts and a Zener knee current of 0.5 mA. The maximum load current drawn

from this circuit ensuring proper functioning over the input voltage range

between 20 and 30 Volts, is

4

GATE ECE 2005

MCQ (Single Correct Answer)

+2

-0.6

A Silicon PN junction diode under reverse bias has depletion region of width 10

µm. The relative permittivity of Silicon, ɛr = 11.7 and the permittivity of free space ɛ0 = 8.854 × 10-12 F/m.The depletion capacitance of the diode per square meter is

Questions Asked from PN Junction (Marks 2)

Number in Brackets after Paper Indicates No. of Questions

GATE ECE 2025 (1)

GATE ECE 2024 (1)

GATE ECE 2022 (1)

GATE ECE 2017 Set 2 (1)

GATE ECE 2016 Set 2 (1)

GATE ECE 2016 Set 3 (1)

GATE ECE 2015 Set 1 (1)

GATE ECE 2015 Set 3 (1)

GATE ECE 2014 Set 2 (1)

GATE ECE 2013 (1)

GATE ECE 2009 (1)

GATE ECE 2007 (1)

GATE ECE 2005 (2)

GATE ECE 2003 (2)

GATE ECE 1993 (1)

GATE ECE 1992 (1)

GATE ECE 1991 (2)

GATE ECE 1987 (1)

GATE ECE Subjects

Signals and Systems

Representation of Continuous Time Signal Fourier Series Discrete Time Signal Fourier Series Fourier Transform Discrete Time Signal Z Transform Continuous Time Linear Invariant System Transmission of Signal Through Continuous Time LTI Systems Discrete Time Linear Time Invariant Systems Sampling Continuous Time Signal Laplace Transform Discrete Fourier Transform and Fast Fourier Transform Transmission of Signal Through Discrete Time Lti Systems Miscellaneous Fourier Transform

Network Theory

Control Systems

Digital Circuits

General Aptitude

Electronic Devices and VLSI

Analog Circuits

Engineering Mathematics

Microprocessors

Communications

Electromagnetics