1

GATE ECE 2002

MCQ (Single Correct Answer)

+2

-0.6

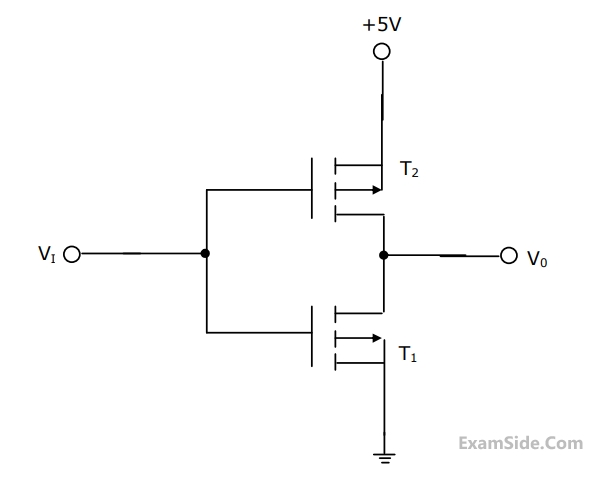

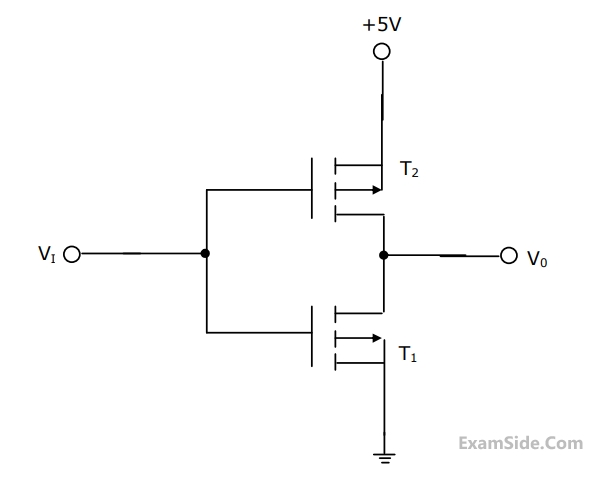

Consider the following statements in connection with the CMOS inverter in the Figure.

Where both the MOSFETS are of enhancement type and both have a threshold voltage of 2V.

Statement 1: T1 conducts when Vi $$ \ge \,2\,V$$.

Statement 2: T1 is always in saturation when $${V_0}\, = \,0\,V$$.

Which of the following is correct?

2

GATE ECE 1992

MCQ (Single Correct Answer)

+2

-0.6

An n-channel JFET has a pinch-off voltage of Vp = -5V. VDS(max) = 20V and gm = 2mA/V. The minimum 'ON' resistance is achieved in the JFET for

3

GATE ECE 1992

MCQ (Single Correct Answer)

+2

-0.6

The JFET in the circuit shown in fig. has an IDSS = 10mA and Vp = -5V. The value of the resistance Rs for a drain current IDS = 6.4mA is (select the Nearest value).

Questions Asked from FET and MOSFET (Marks 2)

Number in Brackets after Paper Indicates No. of Questions

GATE ECE Subjects

Network Theory

Control Systems

Electronic Devices and VLSI

Analog Circuits

Digital Circuits

Microprocessors

Signals and Systems

Representation of Continuous Time Signal Fourier Series Fourier Transform Continuous Time Signal Laplace Transform Discrete Time Signal Fourier Series Fourier Transform Discrete Fourier Transform and Fast Fourier Transform Discrete Time Signal Z Transform Continuous Time Linear Invariant System Discrete Time Linear Time Invariant Systems Transmission of Signal Through Continuous Time LTI Systems Sampling Transmission of Signal Through Discrete Time Lti Systems Miscellaneous

Communications

Electromagnetics

General Aptitude