1

GATE ECE 2017 Set 1

Numerical

+2

-0

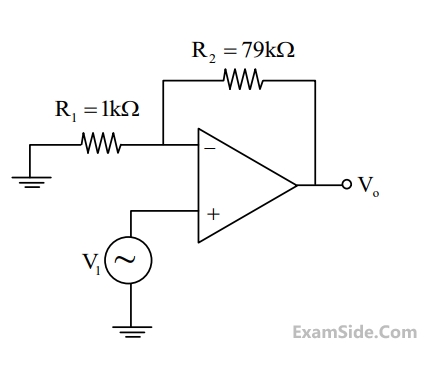

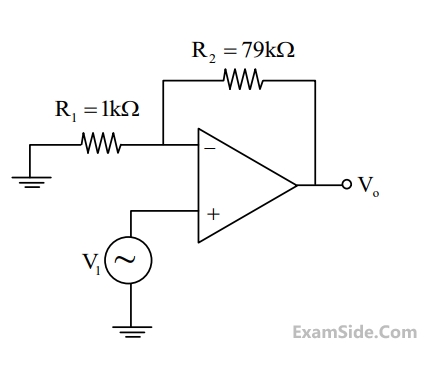

The amplifier circuit shown in the figure is

implemented using a compensated operational

amplifier (op-amp), and has an open-loop voltage

gain, A0 105 V/V and an open-loop cut-off frequency, fC = 8 Hz. The voltage gain of the amplifier

at 15 kHz, in V/V, is __________.

Your input ____

2

GATE ECE 2016 Set 3

Numerical

+2

-0

For the circuit shown in the figure, R1 = R2 = R3 = 1 Ω, L = 1 µH and C = 1 µF. If the input Vin = cos(106t) , then the overall voltage gain (Vout /Vin) of the circuit is __________.

Your input ____

3

GATE ECE 2016 Set 2

Numerical

+2

-0

An opamp has a finite open loop voltage gain of 100. Its input offset voltage Vios (= +5mV) is

modeled as shown in the circuit below. The amplifier is ideal in all other respects. Vinput is 25 mV.

The output voltage (in millivolts) is ________.

Your input ____

4

GATE ECE 2016 Set 2

Numerical

+2

-0

In the opamp circuit shown, the Zener diodes Z1 and Z2 clamp the output voltage Vo to +5 V or -5 V. The switch S is intially closed and is opened at time t = 0

The time t = t1 (in seconds) at which Vo changes state is _____.

Your input ____

Questions Asked from Operational Amplifier (Marks 2)

Number in Brackets after Paper Indicates No. of Questions

GATE ECE 2024 (2)

GATE ECE 2023 (2)

GATE ECE 2022 (1)

GATE ECE 2017 Set 2 (1)

GATE ECE 2017 Set 1 (1)

GATE ECE 2016 Set 3 (1)

GATE ECE 2016 Set 2 (2)

GATE ECE 2016 Set 1 (2)

GATE ECE 2015 Set 2 (2)

GATE ECE 2015 Set 3 (1)

GATE ECE 2015 Set 1 (2)

GATE ECE 2014 Set 1 (2)

GATE ECE 2014 Set 3 (1)

GATE ECE 2013 (1)

GATE ECE 2012 (1)

GATE ECE 2008 (3)

GATE ECE 2007 (4)

GATE ECE 2006 (1)

GATE ECE 2005 (4)

GATE ECE 2004 (1)

GATE ECE 2003 (3)

GATE ECE 2001 (3)

GATE ECE 2000 (1)

GATE ECE 1997 (1)

GATE ECE 1993 (1)

GATE ECE 1992 (3)

GATE ECE 1990 (3)

GATE ECE 1989 (1)

GATE ECE 1988 (1)

GATE ECE 1987 (1)

GATE ECE Subjects

Signals and Systems

Representation of Continuous Time Signal Fourier Series Fourier Transform Continuous Time Signal Laplace Transform Discrete Time Signal Fourier Series Fourier Transform Discrete Fourier Transform and Fast Fourier Transform Discrete Time Signal Z Transform Continuous Time Linear Invariant System Discrete Time Linear Time Invariant Systems Transmission of Signal Through Continuous Time LTI Systems Sampling Transmission of Signal Through Discrete Time Lti Systems Miscellaneous

Network Theory

Control Systems

Digital Circuits

General Aptitude

Electronic Devices and VLSI

Analog Circuits

Engineering Mathematics

Microprocessors

Communications

Electromagnetics