1

GATE ECE 2005

MCQ (Single Correct Answer)

+2

-0.6

What memory address range is NOT represented by chip 1 and chip 2 in

figure? A0 to A15 in this figure are the address lines and CS means Chip Select.

2

GATE ECE 2005

MCQ (Single Correct Answer)

+2

-0.6

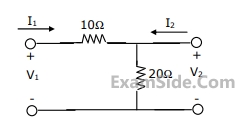

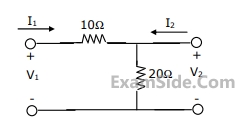

The h parameters of the circuit shown in Fig. are

3

GATE ECE 2005

MCQ (Single Correct Answer)

+1

-0.3

The ABCD parameters of an ideal n:1 transformer shown in Fig. are $$\left[ {\matrix{

n & 0 \cr

0 & X \cr

} } \right]$$. The value of X will be

4

GATE ECE 2005

MCQ (Single Correct Answer)

+2

-0.6

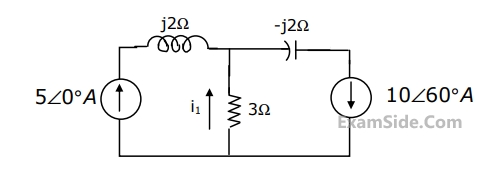

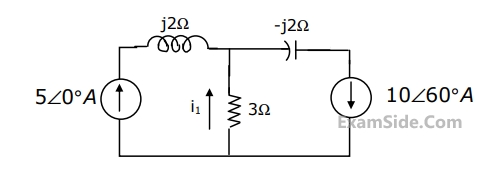

For the circuit in figure, the phase current $${{\rm I}_1}$$ is

Paper analysis

Total Questions

Analog Circuits

13

Communications

8

Control Systems

10

Digital Circuits

7

Electromagnetics

8

Electronic Devices and VLSI

7

Engineering Mathematics

11

Microprocessors

3

Network Theory

10

Signals and Systems

14

More papers of GATE ECE

GATE ECE 2025

GATE ECE 2024

GATE ECE 2023

GATE ECE 2022

GATE ECE 2021

GATE ECE 2019

GATE ECE 2018

GATE ECE 2017 Set 1

GATE ECE 2017 Set 2

GATE ECE 2016 Set 2

GATE ECE 2016 Set 1

GATE ECE 2016 Set 3

GATE ECE 2015 Set 2

GATE ECE 2015 Set 1

GATE ECE 2015 Set 3

GATE ECE 2014 Set 4

GATE ECE 2014 Set 3

GATE ECE 2014 Set 2

GATE ECE 2014 Set 1

GATE ECE 2013

GATE ECE 2012

GATE ECE 2011

GATE ECE 2010

GATE ECE 2009

GATE ECE 2008

GATE ECE 2007

GATE ECE 2006

GATE ECE 2005

GATE ECE 2004

GATE ECE 2003

GATE ECE 2002

GATE ECE 2001

GATE ECE 2000

GATE ECE 1999

GATE ECE 1998

GATE ECE 1997

GATE ECE 1996

GATE ECE 1995

GATE ECE 1994

GATE ECE 1993

GATE ECE 1992

GATE ECE 1991

GATE ECE 1990

GATE ECE 1989

GATE ECE 1988

GATE ECE 1987

GATE ECE

Papers

2025

2024

2023

2022

2021

2019

2018

2014

2013

2012

2011

2010

2009

2008

2007

2006

2005

2004

2003

2002

2001

2000

1999

1998

1997

1996

1995

1994

1993

1992

1991

1990

1989

1988

1987