1

GATE CSE 2011

MCQ (Single Correct Answer)

+2

-0.6

Consider the following circuit involving three Dtypes flip-flops used in a certain type of Counter configuration.

If at some instance prior to the occurrence of the clock edge, $$P, Q$$ and $$R$$ have a value $$0,1$$ and $$0$$ respectively, what shall be the value of $$PQR$$ after the clock edge?

2

GATE CSE 2011

MCQ (Single Correct Answer)

+2

-0.6

Consider the following circuit involving three Dtypes flip-flops used in a certain type of Counter configuration.

If all the flip-flops were reset to $$0$$ at power on, what is the total number of distinct outputs (states) represented by $$PQR$$ generated by the counter?

3

GATE CSE 2009

MCQ (Single Correct Answer)

+2

-0.6

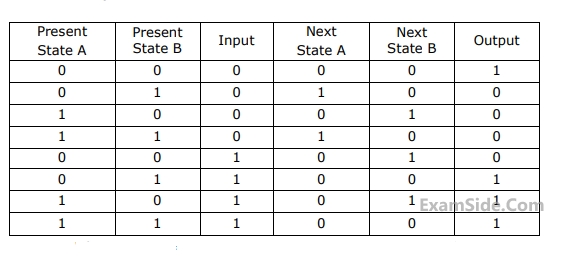

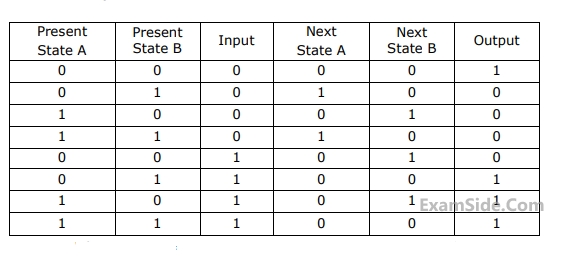

Given the following state table of an $$FSM$$ with two states $$A$$ and $$B,$$ one input and one output:

If the initial state is $$A = 0, B=0.$$ What is the minimum length of an input string which will take the machine to the state $$A=0, B=1$$ with Output$$=1?$$

4

GATE CSE 2007

MCQ (Single Correct Answer)

+2

-0.6

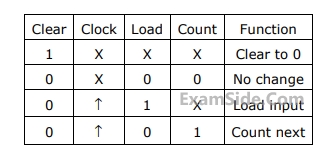

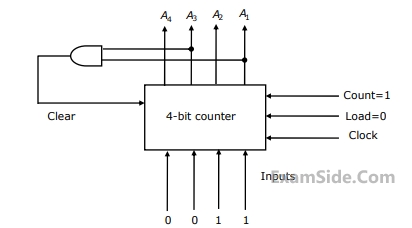

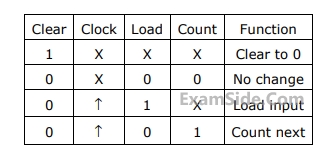

The control signal functions of a $$4$$-bit binary counter are given below $$($$where $$X$$ “don’t care”$$):$$

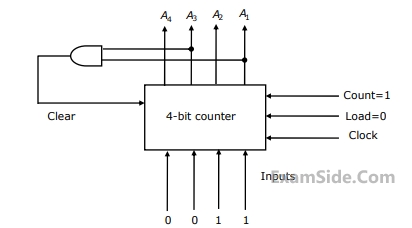

The counter is connected as follows:

Assume that the counter and gate delays are negligible. If the counter starts at $$0,$$ then it cycles through the following sequence:

Questions Asked from Sequential Circuits (Marks 2)

Number in Brackets after Paper Indicates No. of Questions

GATE CSE 2025 Set 1 (1)

GATE CSE 2023 (1)

GATE CSE 2022 (1)

GATE CSE 2021 Set 2 (1)

GATE CSE 2021 Set 1 (1)

GATE CSE 2015 Set 1 (1)

GATE CSE 2014 Set 3 (1)

GATE CSE 2011 (2)

GATE CSE 2009 (1)

GATE CSE 2007 (1)

GATE CSE 2006 (1)

GATE CSE 2004 (1)

GATE CSE 2003 (1)

GATE CSE 2001 (2)

GATE CSE 2000 (1)

GATE CSE 1991 (1)

GATE CSE Subjects

Theory of Computation

Operating Systems

Algorithms

Database Management System

Data Structures

Computer Networks

Software Engineering

Compiler Design

Web Technologies

General Aptitude

Discrete Mathematics

Programming Languages