Pipelining · Computer Organization · GATE CSE

Marks 1

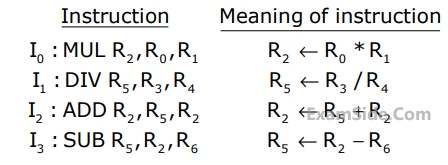

An instruction format has the following structure:

Instruction Number: Opcode destination reg, source reg-1, source reg-2

Consider the following sequence of instructions to be executed in a pipelined processor:

I1: DIV R3, R1, R2

I2: SUB R5, R3, R4

I3: ADD R3, R5, R6

I4: MUL R7, R3, R8

Which of the following statements is/are TRUE?

Consider a 5-stage pipelined processor with Instruction Fetch (IF), Instruction Decode (ID), Execute (EX), Memory Access (MEM), and Register Writeback (WB) stages. Which of the following statements about forwarding is/are CORRECT?

Consider a 3-stage pipelined processor having a delay of 10 ns (nanoseconds), 20 ns, and 14 ns, for the first, second, and the third stages, respectively. Assume that there is no other delay and the processor does not suffer from any pipeline hazards. Also assume that one instruction is fetched every cycle.

The total execution time for executing 100 instructions on this processor is ___________ ns.

$$1.\,\,\,\,\,$$ The $$j+1$$ instruction uses the result of the $$j$$-$$th$$ instruction as an operand

$$2.\,\,\,\,\,$$ The execution of a conditional jump instruction

$$3.\,\,\,\,\,$$ The $$j$$-$$th$$ and $$j+1$$ instruction require the $$ALU$$ at the same time

Which of the above can cause a hazard?

Marks 2

A 5-stage instruction pipeline has stage delays of $180,250,150,170$, and 250 , respectively, in nanoseconds. The delay of an inter-stage latch is 10 nanoseconds. Assume that there are no pipeline stalls due to branches and other hazards. The time taken to process 1000 instructions in microseconds is ________ . (Rounded off to two decimal places)

An application executes $6.4 \times 10^8$ number of instructions in 6.3 seconds. There are four types of instructions, the details of which are given in the table. The duration of a clock cycle in nanoseconds is _________. (rounded off to one decimal place)

| Instruction type |

Clock cycles required per instruction (CPI) |

Number of Instructions executed |

|---|---|---|

| Branch | 2 | $2.25\times10^8$ |

| Load | 5 | $1.20\times10^8$ |

| Store | 4 | $1.65\times10^8$ |

| Arithmetic | 3 | $1.30\times10^8$ |

A non-pipelined instruction execution unit operating at 2 GHz takes an average of 6 cycles to execute an instruction of a program P. The unit is then redesigned to operate on a 5-stage pipeline at 2 GHz. Assume that the ideal throughput of the pipelined unit is 1 instruction per cycle. In the execution of program P, 20% instructions incur an average of 2 cycles stall due to data hazards and 20% instructions incur an average of 3 cycles stall due to control hazards. The speedup (rounded off to one decimal place) obtained by the pipelined design over the non-pipelined design is ________

The baseline execution time of a program on a 2 GHz single core machine is 100 nanoseconds (ns). The code corresponding to 90% of the execution time can be fully parallelized. The overhead for using an additional core is 10 ns when running on a multicore system. Assume that all cores in the multicore system run their share of the parallelized code for an equal amount of time.

$$ \text { The number of cores that minimize the execution time of the program is _______. } $$A processor X1 operating at 2 GHz has a standard 5-stage RISC instruction pipeline having a base CPI (cycles per instruction) of one without any pipeline hazards. For a given program P that has 30% branch instructions, control hazards incur 2 cycles stall for every branch. A new version of the processor X2 operating at same clock frequency has an additional branch predictor unit (BPU) that completely eliminates stalls for correctly predicted branches. There is neither any savings nor any additional stalls for wrong predictions. There are no structural hazards and data hazards for X1 and X2. If the BPU has a prediction accuracy of 80%, the speed up (rounded off to two decimal places) obtained by X2 over X1 in executing P is ____________.

Consider a pipelined processor with 5 stages, Instruction Fetch (IF), Instruction Decode (ID), Execute (EX), Memory Access (MEM), and Write Back (WB). Each stage of the pipeline, except the EX stage, takes one cycle. Assume that the ID stage merely decodes the instruction and the register read is performed in the EX stage. The EX stage takes one cycle for ADD instruction and two cycles for MUL instruction. Ignore pipeline register latencies.

Consider the following sequence of 8 instructions:

ADD, MUL, ADD, MUL, ADD, MUL, ADD, MUL

Assume that every MUL instruction is data-dependent on the ADD instruction just before it and every ADD instruction (except the first ADD) is data-dependent on the MUL instruction just before it. The speedup is defined as follows:

$$Speedup = \frac{{Execution{\:}time{\:}without{\:}operand{\:}forwarding}}{{Execution{\:}time{\:}with{\:}operand{\:}forwarding}}$$

The Speedup achieved in executing the given instruction sequence on the pipelined processor (rounded to 2 decimal places) is _______

A five-stage pipeline has stage delays of 150, 120, 150, 160 and 140 nanoseconds. The registers that are used between the pipeline stages have a delay of 5 nanoseconds each.

The total time to execute 100 independent instructions on this pipeline, assuming there are no pipeline stalls, is ______ nanoseconds.

Consider the following instruction sequence where register R1, R2 and R3 are general purpose and MEMORY[X] denotes the content at the memory location X.

|

Instruction |

Semantics |

Instruction Size (bytes) |

|

MOV R1, (5000) |

R1 ← MEMORY[5000] |

4 |

|

MOV R2, (R3) |

R2 ← MEMORY[R3] |

4 |

|

ADD R2, R1 |

R2 ← R1 + R2 |

2 |

|

MOV (R3), R2 |

MEMORY[R3] ← R2 |

4 |

|

INC R3 |

R3 ← R3 + 1 |

2 |

|

DEC R1 |

R1 ← R1 – 1 |

2 |

|

BNZ 1004 |

Branch if not zero to the given absolute address |

2 |

|

HALT |

Stop |

1 |

Assume that the content of the memory location 5000 is 10, and the content of the register R3 is 3000. The content of each of the memory locations from 3000 to 3010 is 50. The instruction sequence starts from the memory location 1000. All the numbers are in decimal format. Assume that the memory is byte addressable.

After the execution of the program, the content of memory location 3010 is ______

The number of clock cycles required for completion of execution of the sequence of instructions is ______.

The minimum average latency $$(MAL)$$ is ________.

| MUL | R5, R0, R1 |

|---|---|

| DIV | R6, R2, R3 |

| ADD | R7, R5, R6 |

| SUB | R8, R7, R4 |

In the above sequence, $$R0$$ to $$R8$$ are general purpose registers. In the instructions shown, the first register stores the result of the operation performed on the second and the third registers. This sequence of instructions is to be executed in a pipelined instruction processor with the following $$4$$ stages: $$(1)$$ Instruction Fetch and Decode $$(IF), (2)$$ Operand Fetch $$(OF), (3)$$ Perform Operation $$(PO)$$ and $$(4)$$ Write back the result $$(WB).$$ The $$IF,$$ $$OF$$ and $$WB$$ stages take $$1$$ clock cycle each for any instruction. The $$PO$$ stage takes $$1$$ clock cycle for $$ADD$$ or $$SUB$$ instruction, $$3$$ clock cycles for $$MUL$$ instruction and $$5$$ clock cycles for $$DIV$$ instruction. The pipelined processor uses operand forwarding from the $$PO$$ stage to the $$OF$$ stage. The number of clock cycles taken for the execution of the above sequence of instructions is _______________________ .

$$P1:$$ Four-stage pipeline with stage latencies $$1$$ $$ns,$$ $$2$$ $$ns,$$ $$2$$ $$ns,$$ $$1$$ $$ns.$$

$$P2:$$ Four-stage pipeline with stage latencies $$1$$ $$ns,$$ 1$$.5$$ $$ns,$$ $$1.5$$ $$ns,$$ $$1.5$$ $$ns.$$

$$P3:$$ Five-stage pipeline with stage latencies $$0.5$$ $$ns,$$ $$1$$ $$ns,$$ $$1$$ $$ns,$$ $$0.6$$ $$ns,$$ $$1$$ $$ns.$$

$$P4:$$ Five-stage pipeline with stage latencies $$0.5$$ $$ns,$$ $$0.5$$ $$ns,$$ $$1$$ $$ns,$$ $$1$$ $$ns,$$ $$1.1$$ $$ns.$$

Which processor has the highest peak clock frequency?

What is the approximate speed up of the pipeline in steady state under ideal conditions when compared to the corresponding non-pipeline implementation?

What is the number of cycles needed to execute the following loop?

For $$\left( {i = 1} \right.$$ to $$\left. 2 \right)$$ $$\left\{ {{\rm I}1;{\rm I}2;{\rm I}3;{\rm I}4;} \right\}$$

$$\eqalign{ & {{\rm I}_1}:\,\,ADD\,\,{R_2}\,\, \leftarrow \,\,{R_7} + {R_8} \cr & {{\rm I}_2}:\,\,SUB\,\,\,{R_4}\,\, \leftarrow \,\,{R_5} - {R_6} \cr & {{\rm I}_3}:\,\,ADD\,\,{R_1}\,\, \leftarrow \,\,{R_2} + {R_3} \cr & {{\rm I}_4}:\,\,STORE\,\,Memory\,\,\left[ {{R_4}} \right]\,\, \leftarrow \,\,{R_1} \cr & BRANCH\,\,to\,\,Label\,\,if\,\,{R_1} = = 0 \cr} $$

Which of the instructions $${{\rm I}_1},\,{{\rm I}_2},\,{{\rm I}_3}$$ or $${{\rm I}_4}$$ can legitimately occupy the delay slot without any other program modification?

$$1.$$ Bypassing can handle all RAW hazards

$$2.$$ Register renaming can eliminate all register carried WAR hazards

$$3.$$ Control hazard penalties can be eliminated by dynamic branch prediction.

$$1.\,\,\,\,$$ Function locals and parameters

$$2.\,\,\,\,$$ Register saves and restores

$$3.\,\,\,\,$$ Instruction fetches

$$\,\,\,\,\,$$$$IF:$$ Instruction Fetch

$$\,\,\,\,\,$$$$ID:$$ Instruction Decode and Operand Fetch

$$\,\,\,\,\,$$$$EX:$$ Execute

$$\,\,\,\,\,$$$$WB:$$ Write Back

The $$IF, ID$$ and $$WB$$ stages take one clock cycle each to complete the operation. The number of clock cycles for the $$EX$$ stage depends on the instruction. The $$ADD$$ and $$SUB$$ instructions need $$1$$ clock cycle and the $$MUL$$ instruction needs $$3$$ clock cycles in the $$EX$$ stage. Operand forwarding is used in the pipelined processor. What is the number of clock cycles taken to complete the following sequence of instructions?

Consider the following sequence of instructions:

$$\eqalign{

& {{\rm I}_1}:L\,R0,\,\,Loc1;\,R0 < \,\, = M\,[Loc1] \cr

& {{\rm I}_2}:A\,R0,\,R0;\,\,\,\,\,\,R0 < \,\, = R0 + R0 \cr

& {{\rm I}_3}:A\,R2,\,R0;\,\,\,\,\,\,R2 < \,\, = R2 - R0 \cr} $$

Let each stage takes one clock cycle.

What is the number of clock cycles taken to complete the above sequence of instructions starting from the fetch of $${{\rm I}_1}?$$

Marks 5

(a) Calculate the average instruction execution time assuming that $$20$$% of all instruction executed are branch instructions. Ignore the fact that some branch instructions may be conditional.

(b) If a branch instruction is a conditional branch instruction, the branch need not be taken. If the branch is not taken, the following instructions can be overlapped. When $$80$$% of all branch instructions are conditional branch instructions, and $$50$$% of the conditional branch instructions are such that the branch is taken, calculate the average instruction execution time.

Find the number of clock cycles needed to perform the $$5$$ instructions