Combinational Circuits · Digital Logic · GATE CSE

Marks 1

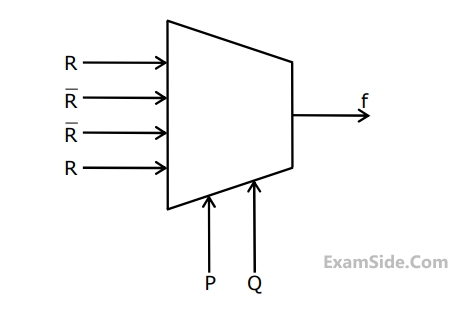

Consider the following logic circuit diagram.

Which is/are the CORRECT option(s) for the output function?

Consider the circuit shown below where the gates may have propagation delays. Assume that all signal transitions occur instantaneously and that wires have no delays. Which of the following statements about the circuit is/are CORRECT?

Which one of the following circuits implements the Boolean function given below?

f(x, y, z) = m0 + m1 + m3 + m4 + m5 + m6, where mi is the ith minterm.

What function does the truth table represent?

Marks 2

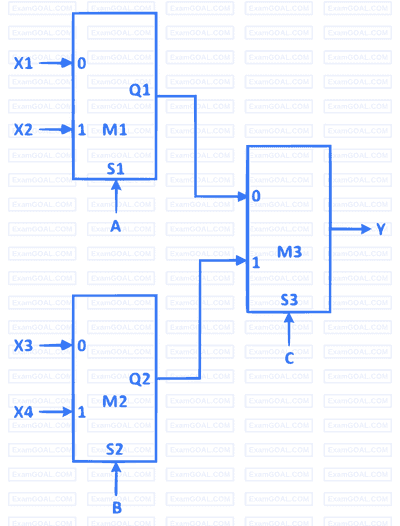

Consider a digital logic circuit consisting of three 2-to-1 multiplexers M1, M2, and M3 as shown below. X1 and X2 are inputs of M1. X3 and X4 are inputs of M2. A, B, and C are select lines of M1, M2, and M3, respectively.

For an instance of inputs X1=1, X2=1, X3=0, and X4=0, the number of combinations of A, B, C that give the output Y=1 is ______________

A Boolean digital circuit is composed using two 4-input multiplexers (M1 and M2) and one 2-input multiplexer (M3) as shown in the figure. X0-X7 are the inputs of the multiplexers M1 and M2 and could be connected to either 0 or 1. The select lines of the multiplexers are connected to Boolean variables A, B and C as shown.

Which one of the following set of values of (X0, X1, X2, X3, X4, X5, X6, X7) will realise the Boolean function $$\overline A + \overline A \,.\,\overline C + A\,.\,\overline B \,.\,C$$ ?

The minimal sum of products form of the output $$X$$ is

The minimal sum-of-products form of the Boolean expression for the output $$F$$ of the multiplexer is

If the operands are in $$2's$$ complement representation, which of the following operations can be performed by suitably setting the control lines $$K$$ and $${C_0}$$ only ( + and - denote addition and subtraction respectively)?

The function $$f(x,y,z)$$ implemented by the above circuit is

Which of the following is true?

In the two bit full-adder/sub tractor unit shown in Fig., when the switch is in position $$2.$$ $$.....$$ using $$.....$$ arithmetic.