Machine Instructions and Addressing Modes · Computer Organization · GATE CSE

Marks 1

Which of the following is/are part of an Instruction Set Architecture of a processor?

I. Daisy chaining is used to assign priorities in attending interrupts.

II. When a device raises a vectored interrupt, the CPU does polling to identify the source of the interrupt.

III. In polling, the CPU periodically checks the status bits to know if any device needs its attention.

IV. During DMA, both the CPU and DMA controller can be bus masters at the same time.

Which of the above statements is/are TRUE?

(S1) A memory operand

(S2) A processor register

(S3) An implied accumulator register

$$1.$$ Absolute addressing

$$2.$$ Based addressing

$$3.$$ Relative addressing

$$4.$$ Indirect addressing

$$X:$$ Indirect addressing

$$Y:$$ Immediate addressing

$$Z:$$ Auto decrement addressing is

$$1:$$ Loops

$$2:$$ Pointers

$$3.$$ Constants

Marks 2

A processor has 64 general-purpose registers and 50 distinct instruction types. An instruction is encoded in 32-bits. What is the maximum number of bits that can be used to store the immediate operand for the given instruction?

$$\mathrm{ADD ~ R1,~\#25 \qquad // R1 = R1 + 25}$$

A processor with 16 general purpose registers uses a 32-bit instruction format. The instruction format consists of an opcode field, an addressing mode field, two register operand fields, and a 16-bit scalar field. If 8 addressing modes are to be supported, the maximum number of unique opcodes possible for every addressing mode is _________

A processor uses a 32-bit instruction format and supports byte-addressable memory access. The ISA of the processor has 150 distinct instructions. The instructions are equally divided into two types, namely R-type and I-type, whose formats are shown below.

R-type Instruction Format:

| OPCODE | UNUSED | DST Register | SRC Register1 | SRC Register2 |

|---|

I-type Instruction Format:

| OPCODE | DST Register | SRC Register | # Immediate value/address |

|---|

In the OPCODE, 1 bit is used to distinguish between I-type and R-type instructions and the remaining bits indicate the operation. The processor has 50 architectural registers, and all register fields in the instructions are of equal size.

Let X be the number of bits used to encode the UNUSED field, Y be the number of bits used to encode the OPCODE field, and Z be the number of bits used to encode the immediate value/address field. The value of X + 2Y + Z is __________.

Consider the given C-code and its corresponding assembly code, with a few operands U1-U4 being unknown. Some useful information as well as the semantics of each unique assembly instruction is annotated as inline comments in the code. The memory is byte-addressable.

Which one of the following options is a CORRECT replacement for operands in the position (U1, U2, U3, U4) in the above assembly code?

The maximum value of $$N$$ is __________.

$$\,\,\,\,\,\,\,\,\,\,\,\,\,\,OP\,\,Ri,\,\,Rj,\,\,Rk$$

where operation $$OP$$ is performed on contents of registers $$Rj$$ and $$Rk$$ and the result is stored in register $$Ri.$$

$$\eqalign{ & \,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,{I_1}:ADD\,\,\,R1,\,R2,\,R3 \cr & \,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,{I_2}:MUL\,\,R7,\,R1,\,R3 \cr & \,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,{I_3}:SUB\,\,\,\,R4,\,R1,\,R5 \cr & \,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,{I_4}:ADD\,\,\,R3,\,R2,\,R4 \cr & \,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,\,{I_5}:MUL\,\,\,R7,\,R8,\,R9 \cr} $$

Consider the following three statements.

$$\,\,\,\,\,\,S1:\,\,$$ There is an anti-dependence between instructions $${L_2}$$ and $${L_5}$$

$$\,\,\,\,\,\,S2:\,\,$$ There is an anti-dependence between instructions $${L_2}$$ and $${L_4}$$

$$\,\,\,\,\,\,S3:\,\,$$ Within an instruction pipeline an anti-dependence always creates one or more stalls

Which one of above statements is/are correct?

$$ \bullet \,\,\,\,\,\,\,\,$$ Store the current value of $$PC$$ in the stack

$$ \bullet \,\,\,\,\,\,\,\,$$ Store the value of $$PSW$$ register in the stack

$$ \bullet \,\,\,\,\,\,\,\,$$ Load the starting address of the subroutine in $$PC$$

The content of $$PC$$ just before the fetch of a CALL instruction is $$\left( {5FA0} \right){\,_{16}}.$$ After execution of the CALL instruction, the value of the stack pointer is

$$LOOP:$$ Load a byte from device Store in memory at address given by address register

Increment the address register

Decrement the count

If count! $$=0$$ go to $$LOOP$$

Assume that each statement in this program is equivalent to a machine instruction which takes one clock cycle to execute if it is a non load/store instruction. The load-store instructions take two clock cycles to execute.

The designer of the system also has an alternate approach of using the $$DMA$$ controller to implement the same transfer. The $$DMA$$ controller requires $$20$$ clock cycles for initialization and other overheads. Each $$DMA$$ transfer cycle takes two clock cycles to transfer one byte of data from the device to the memory.

What is the approximate speed up when the $$DMA$$ controller based design is used in place of the interrupt driven program based input- output?

$$1.$$ It must be a trap instruction

$$2.$$ It must be a privileged instruction

$$3.$$ An exception cannot be allowed to occur during execution of an $$RFE$$ instruction.

$$1.$$ It is useful in creating self relocating code

$$2.$$ If it is included in an Instruction Set Architecture, then an additional $$ALU$$ is required for effective address calculation

$$3.$$ The amount of increment depends on the size of the data item accessed.

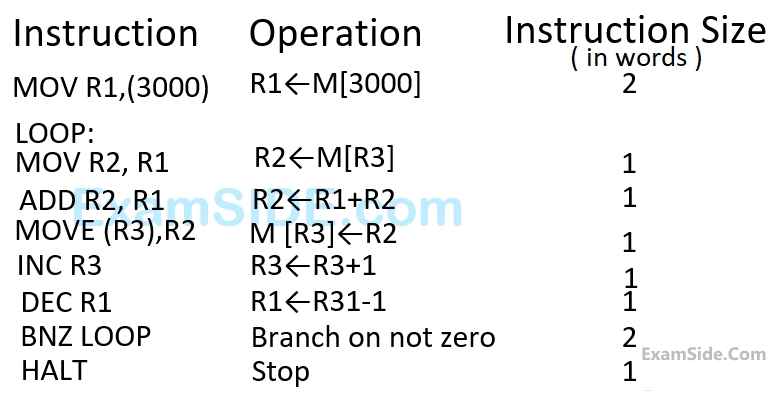

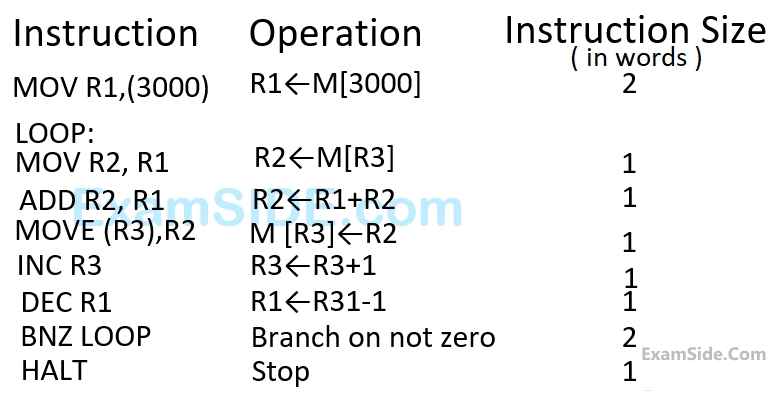

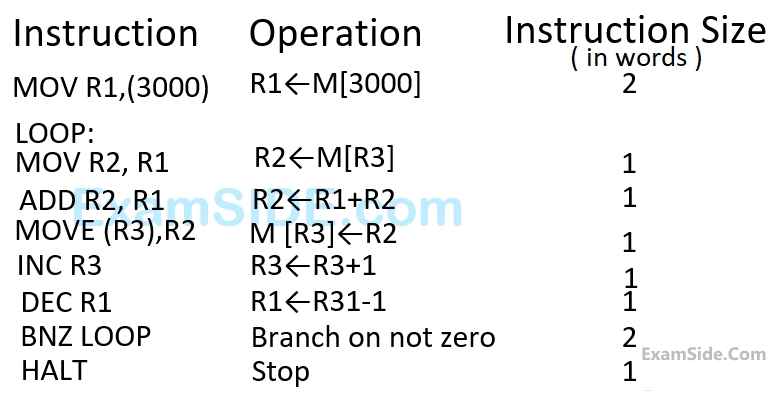

Assume that the content of memory location $$3000$$ is $$10$$ and the content of the register $$R3$$ is $$2000$$. The content of each of the memory locations from $$2000$$ to $$2010$$ is $$100.$$ The program is loaded from the memory location $$1000.$$ All the numbers are in decimal.

Assume that the memory is word addressable. The number of memory references for accessing the data in executing the program completely is

Assume that the content of memory location $$3000$$ is $$10$$ and the content of the register $$R3$$ is $$2000$$. The content of each of the memory locations from $$2000$$ to $$2010$$ is $$100.$$ The program is loaded from the memory location $$1000.$$ All the numbers are in decimal.

Assume that the memory is byte addressable and the word size is $$32$$ bits. If an interrupt occurs during the execution of the instruction $$''INC$$ $$R3'',$$ what return address will be pushed on to the stack?

Assume that the content of memory location $$3000$$ is $$10$$ and the content of the register $$R3$$ is $$2000$$. The content of each of the memory locations from $$2000$$ to $$2010$$ is $$100.$$ The program is loaded from the memory location $$1000.$$ All the numbers are in decimal.

Assume that the memory is word addressable. After the execution of this program, the content of memory location $$2010$$ is

The first operand (destination) ''$$A$$ $$\left[ {{R_0}} \right]''$$ uses indexed addressing mode with $${{R_0}}$$ as the index register. The second operand (source) $$''@B''$$ used indirect addressing mode. $$A$$ and $$B$$ are memory addresses residing at the second and the third words, respectively. The first word of the instruction specific the opcode, the index register designation and the source and destination addressing modes. During execution of $$ADD$$ instruction, the two operands are added and stored in the destination (first operand).

The number of memory cycles needed during the execution cycle of the instruction is

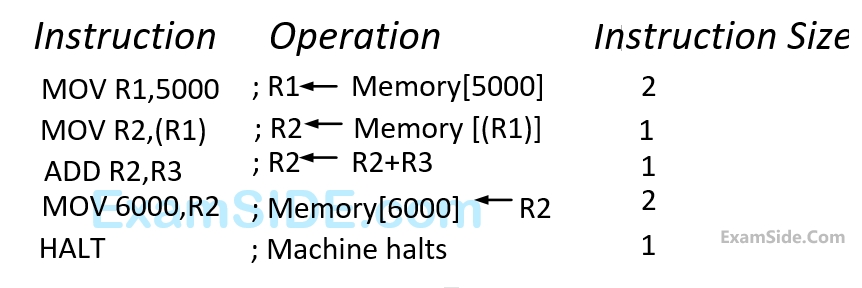

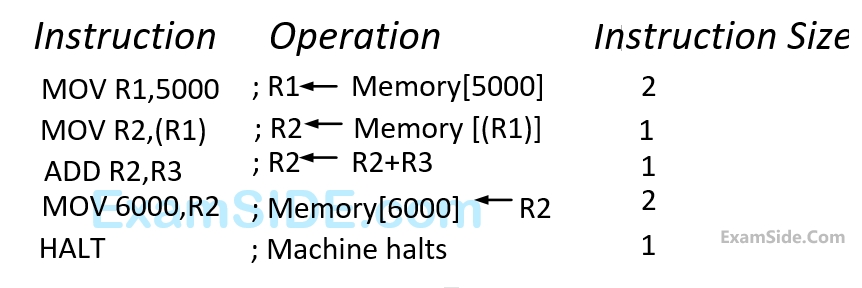

Consider that the memory is byte addressable with word size $$32$$ bits, and the program has been loaded starting from memory location $$1000$$ (decimal). If an interrupt occurs while the $$CPU$$ has been halted after executing the HALT instruction, the return address (in decimal) saved in the stack will be

Let the clock cycles required for various operations be as follows:

Register to/from memory transfer:

$$3$$ clock cycles

ADD with both operands in register:

$$1$$ clock cycle

Instruction fetch and decode:

$$2$$ clock cycles per word

The total number of clock cycle required to execute the program is

$$X.$$ Indirect Addressing

$$Y.$$ Indexed Addressing

$$Z.$$ Base Register Addressing

$${\rm I}.\,\,$$Array implementation

$${\rm II}.\,\,$$Writing relocatable code

$${\rm III}.\,\,$$Passing array as parameter