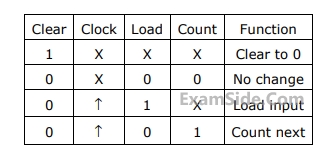

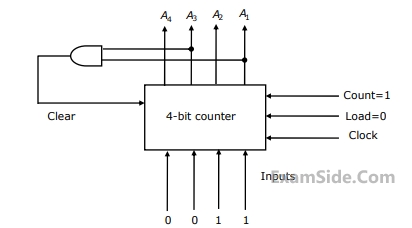

The counter is connected as follows:

Assume that the counter and gate delays are negligible. If the counter starts at $$0,$$ then it cycles through the following sequence:

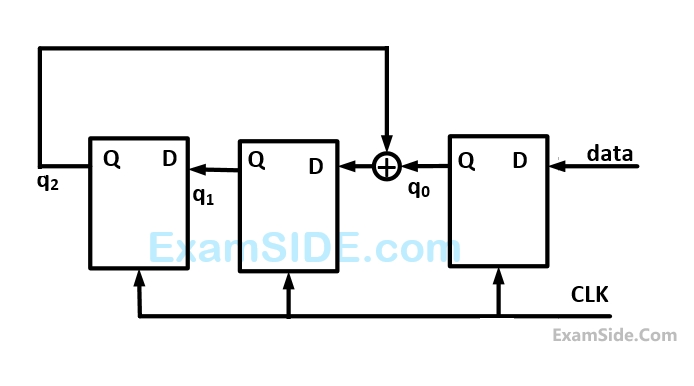

The following data: $$100110000$$ is supplied to the ''data'' terminal in nine clock cycles. After that the values of $${q_2}{q_1}{q_0}$$ are

To complete the circuit, the input $$X$$ should be

Let $${z_k},\,{n_k}$$ denote the number of $$0’s$$ and $$1’s$$ respectively in initial $$k$$ bits of the input

$$\left({{z_k} + {n_k} = k} \right).$$ The circuit outputs $$00$$ until one of the following conditions holds.

$$ * \,\,\,\,\,$$ $${z_k} = {n_k} + 2.\,\,\,$$ In this case, the output at the $$k$$-th and all subsequent clock ticks is $$10.$$

$$ * \,\,\,\,\,$$ $${n_k} = {z_k} + 2.\,\,\,$$ In this case, the output at the $$k$$-th and all subsequent clock ticks is $$01.$$

What is the minimum number of states required in the state transition graph of the above circuit?