1

GATE CSE 2004

MCQ (Single Correct Answer)

+5

-1.5

A circuit outputs a digit in the form of $$4$$ bits. $$0$$ is represented by $$0000$$, $$1$$ by $$0001..., $$ $$9$$ by $$1001.$$ A combinational circuit is to be designed which takes these $$4$$ bits as input and outputs $$1$$ if the digit $$ \ge 5,$$ and $$0$$ otherwise. If only $$AND,$$ $$OR$$ and $$NOT$$ gates may be used, what is the minimum number of gates required?

2

GATE CSE 2003

MCQ (Single Correct Answer)

+5

-1.5

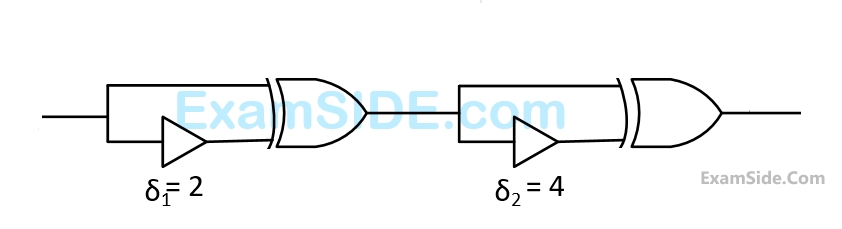

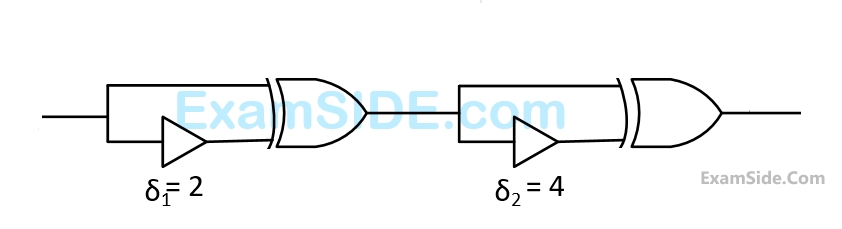

Consider the following circuit composed of $$XOR$$ gates are non-inverting buffers.

The non-inverting buffers have delays $${\delta _1} = 2$$ $$ns$$ and $${\delta _2} = 4$$ $$ns$$ as shown in the figure. Both $$XOR$$ gates and all wires have zero delay. Assume that all gate inputs, outputs and wires are stable at logic level $$0$$ at time$$0.$$ If the following waveform is applied at input $$A$$, how many transition(s) (change of logic levels) occurs(s) at $$B$$ during the interval from $$0$$ to $$10$$ $$ns?$$

3

GATE CSE 2002

Subjective

+5

-0

Express the function $$f( x, y, z)= xy'+ yz'$$ with only one complement operation and one or more $$AND/OR$$ operations. Draw the logic circuit implementing the expression obtained, using a single NOT gate and one or more $$AND/OR$$ gates.

4

GATE CSE 1996

Subjective

+5

-0

A logic network has two data inputs $$A$$ and $$B,$$ and two control inputs $${C_0}$$ and $${C_1}$$. It implements the function $$F$$ according to the following Table.

Implement the circuit using one $$4$$ to $$1$$ Multiplexor, one $$2$$-input Exclusive $$OR$$ gate, one $$2$$-input $$AND$$ gate, one $$2$$-input $$OR$$ gate and one Inverter.

Questions Asked from Boolean Algebra (Marks 5)

Number in Brackets after Paper Indicates No. of Questions

GATE CSE Subjects

Theory of Computation

Operating Systems

Algorithms

Database Management System

Data Structures

Computer Networks

Software Engineering

Compiler Design

Web Technologies

General Aptitude

Discrete Mathematics

Programming Languages