1

GATE CSE 2013

MCQ (Single Correct Answer)

+2

-0.6

Consider an instruction pipeline with five stages without any branch prediction: Fetch Instruction $$(FI),$$ Decode Instruction $$(DI),$$ Fetch Operand $$(FO),$$ Execute Instruction $$(EI)$$ and Write Operand $$(WO).$$ The stage delays for $$FI, DI, FO, EI$$ and $$WO$$ are $$5$$ $$ns,$$ $$7$$ $$ns,$$ $$10$$ $$ns,$$ $$8$$ $$ns$$ and $$6$$ $$ns$$, respectively. There are intermediate storage buffers after each stage and the delay of each buffer is $$1$$ $$ns.$$ A program consisting of $$12$$ instructions $${{\rm I}_1},{{\rm I}_2},{{\rm I}_3},......,\,\,{{\rm I}_{12}}$$ is executed in this pipelined processor. Instruction $${{\rm I}_4}$$ is the only branch instruction and its branch target is $${{\rm I}_9}$$. If the branch is taken during the execution of this program, the time (in $$ns$$) needed to complete the program is

2

GATE CSE 2011

MCQ (Single Correct Answer)

+2

-0.6

Consider an instruction pipeline with four stages $$\left( {S1,\,S2,\,S3,} \right.$$ and $$\left. {S4} \right)$$ each with combinational circuit only. The pipeline registers are required between each stage and at the end of the last stage. Delays for the stages and for the pipeline registers are as given in the figure.

What is the approximate speed up of the pipeline in steady state under ideal conditions when compared to the corresponding non-pipeline implementation?

3

GATE CSE 2010

MCQ (Single Correct Answer)

+2

-0.6

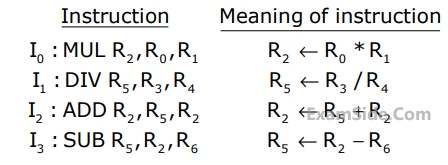

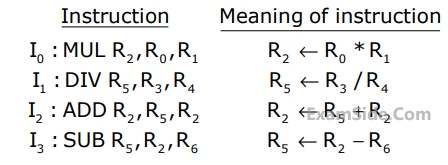

A $$5$$-stage pipelined processor has Instruction Fetch $$(IF),$$ Instruction Decode $$(ID),$$ Operand Fetch $$(OF),$$ Perform Operation $$(PO)$$ and Write Operand $$(WO)$$ stages. The $$IF, ID, OF$$ and $$WO$$ stages take $$1$$ clock cycle each for any instruction. The $$PO$$ stage takes $$1$$ clock cycle for $$ADD$$ and $$SUB$$ instructions, $$3$$ clock cycles for $$MUL$$ instruction, and $$6$$ clock cycles for $$DIV$$ instruction respectively. Operand forwarding is used in the pipeline. What is the number of clock cycles needed to execute the following sequence of instructions?

4

GATE CSE 2009

MCQ (Single Correct Answer)

+2

-0.6

Consider a $$4$$ stage pipeline processor. The number of cycles needed by the four instructions $${\rm I}1,$$ $${\rm I}2,$$ $${\rm I}3,$$ $${\rm I}4,$$ in stages $$S1, S2, S3, S4$$ is shown below.

What is the number of cycles needed to execute the following loop?

For $$\left( {i = 1} \right.$$ to $$\left. 2 \right)$$ $$\left\{ {{\rm I}1;{\rm I}2;{\rm I}3;{\rm I}4;} \right\}$$

Questions Asked from Pipelining (Marks 2)

Number in Brackets after Paper Indicates No. of Questions

GATE CSE 2025 Set 2 (2)

GATE CSE 2024 Set 2 (1)

GATE CSE 2024 Set 1 (1)

GATE CSE 2022 (1)

GATE CSE 2021 Set 2 (1)

GATE CSE 2021 Set 1 (2)

GATE CSE 2020 (1)

GATE CSE 2018 (1)

GATE CSE 2016 Set 1 (1)

GATE CSE 2016 Set 2 (2)

GATE CSE 2015 Set 3 (1)

GATE CSE 2015 Set 1 (1)

GATE CSE 2015 Set 2 (1)

GATE CSE 2014 Set 3 (2)

GATE CSE 2014 Set 1 (1)

GATE CSE 2013 (1)

GATE CSE 2011 (1)

GATE CSE 2010 (1)

GATE CSE 2009 (1)

GATE CSE 2008 (4)

GATE CSE 2007 (1)

GATE CSE 2006 (1)

GATE CSE 2005 (1)

GATE CSE 2004 (1)

GATE CSE 2002 (1)

GATE CSE Subjects

Theory of Computation

Operating Systems

Algorithms

Database Management System

Data Structures

Computer Networks

Software Engineering

Compiler Design

Web Technologies

General Aptitude

Discrete Mathematics

Programming Languages