1

GATE CSE 2011

MCQ (Single Correct Answer)

+2

-0.6

An $$8KB$$ direct-mapped write-back cache is organized as multiple blocks, each of size $$32$$-bytes. The processor generates $$32$$-bit addresses. The cache controller maintains the tag information for each cache block comprising of the following.

$$\,\,\,\,$$$$1$$ Valid bit

$$\,\,\,\,$$$$1$$ Modified bit

$$\,\,\,\,$$$$1$$ Valid bit

$$\,\,\,\,$$$$1$$ Modified bit

As many bits as the minimum needed to identify the memory block mapped in the cache.

What is the total size of memory needed at the cache controller to store meta-data (tags) for the cache?

2

GATE CSE 2010

MCQ (Single Correct Answer)

+2

-0.6

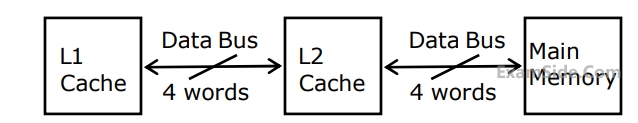

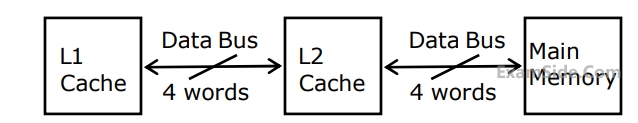

A computer system has an $$L1$$ cache, an $$L2$$ cache, and a main memory unit connected as shown below. The block size in $$L1$$ cache is $$4$$ words. The block size in $$L2$$ cache is $$16$$ words. The memory access times are $$2$$ nanoseconds, $$20$$ nanoseconds and $$200$$ nanoseconds for $$L1$$ cache, $$L2$$ cache and main memory unit respectively.

When there is a miss in $$L1$$ cache and a hit in $$L2$$ cache, a block is transferred from $$L2$$ cache to $$L1$$ cache. What is the time taken for this transfer?

3

GATE CSE 2010

MCQ (Single Correct Answer)

+2

-0.6

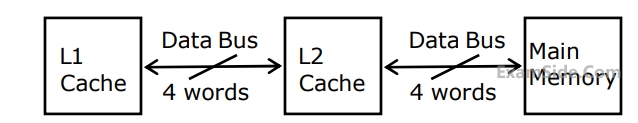

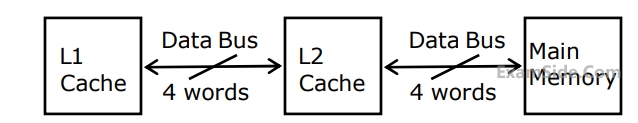

A computer system has an $$L1$$ cache, an $$L2$$ cache, and a main memory unit connected as shown below. The block size in $$L1$$ cache is $$4$$ words. The block size in $$L2$$ cache is $$16$$ words. The memory access times are $$2$$ nanoseconds, $$20$$ nanoseconds and $$200$$ nanoseconds for $$L1$$ cache, $$L2$$ cache and main memory unit respectively.

When there is a miss in both $$L1$$ cache and $$L2$$ cache, first a block is transferred from main memory to $$L2$$ cache, and then a block is transferred from $$L2$$ cache to $$L1$$ cache.

What is the total time taken for these transfers?

4

GATE CSE 2009

MCQ (Single Correct Answer)

+2

-0.6

Consider a $$4$$-way set associative cache (initially empty) with total $$16$$ cache blocks. The main memory consists of $$256$$ blocks and the request for memory blocks is in the following order:

0, 255, 1, 4, 3, 8, 133, 159, 216, 129, 63, 8, 48, 32, 73, 92, 155.

0, 255, 1, 4, 3, 8, 133, 159, 216, 129, 63, 8, 48, 32, 73, 92, 155.

Which one of the following memory block will NOT be in cache if $$LRU$$ replacement policy is used?

Questions Asked from Memory Interfacing (Marks 2)

Number in Brackets after Paper Indicates No. of Questions

GATE CSE 2025 Set 2 (2)

GATE CSE 2025 Set 1 (2)

GATE CSE 2024 Set 1 (2)

GATE CSE 2023 (2)

GATE CSE 2022 (1)

GATE CSE 2021 Set 2 (1)

GATE CSE 2020 (1)

GATE CSE 2019 (1)

GATE CSE 2018 (1)

GATE CSE 2016 Set 2 (2)

GATE CSE 2014 Set 3 (1)

GATE CSE 2014 Set 2 (4)

GATE CSE 2013 (1)

GATE CSE 2012 (2)

GATE CSE 2011 (1)

GATE CSE 2010 (2)

GATE CSE 2009 (1)

GATE CSE 2008 (1)

GATE CSE 2007 (2)

GATE CSE 2006 (3)

GATE CSE 2005 (1)

GATE CSE 2004 (1)

GATE CSE 1990 (1)

GATE CSE Subjects

Theory of Computation

Operating Systems

Algorithms

Database Management System

Data Structures

Computer Networks

Software Engineering

Compiler Design

Web Technologies

General Aptitude

Discrete Mathematics

Programming Languages