1

GATE CSE 2020

Numerical

+1

-0

A direct mapped cache memory of 1 MB has a block ize of 256 bytes. The cache has an access time of 3 ns and a hit rate of 94%. During a cache miss, it takes 20 ns to bring the first word of a block from the main memory, while each subsequent word takes 5 ns. The word size is 64 bits. The average memory access time in ns (round off to 1 decimal place) is _____.

Your input ____

2

GATE CSE 2019

MCQ (Single Correct Answer)

+1

-0.33

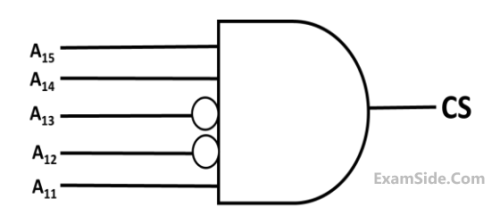

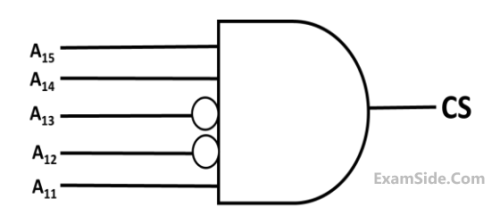

The chip select logic for a certain DRAM chip in a memory system design is shown below. Assume that the memory system has 16 address lines denoted by A15 to A0. What is the range of addresses (in hexadecimal) of the memory system that can get enabled by the chip select (CS) signal?

3

GATE CSE 2019

MCQ (Single Correct Answer)

+1

-0.33

A certain processor uses a fully associative cache of size 16 kB. The cache block size is 16 bytes. Assume that the main memory is byte addressable and uses a 32-bit address. How many bits are required for the Tag and the Index fields resectively in the addresses generated by the processor?

4

GATE CSE 2018

Numerical

+1

-0

A $$32$$-bit wide main memory unit with a capacity of $$1$$ $$GB$$ is built using $$256M\,\, \times \,\,4$$-bit $$DRAM$$ chips. The number of rows of memory cells in the $$DRAM$$ chip is $${2^{14}}.$$ The time taken to perform one refresh operation is $$50$$ nanoseconds. The refresh period is $$2$$ milliseconds. The percentage (rounded to the closest integer) of the time available for performing the memory read/write operations in the main memory unit is __________.

Your input ____

Questions Asked from Memory Interfacing (Marks 1)

Number in Brackets after Paper Indicates No. of Questions

GATE CSE 2022 (1)

GATE CSE 2021 Set 2 (1)

GATE CSE 2021 Set 1 (1)

GATE CSE 2020 (1)

GATE CSE 2019 (2)

GATE CSE 2018 (1)

GATE CSE 2016 Set 1 (1)

GATE CSE 2015 Set 3 (1)

GATE CSE 2015 Set 2 (1)

GATE CSE 2014 Set 1 (1)

GATE CSE 2013 (1)

GATE CSE 2012 (1)

GATE CSE 2010 (1)

GATE CSE 2009 (1)

GATE CSE 2007 (1)

GATE CSE 2005 (1)

GATE CSE 2001 (1)

GATE CSE 1999 (1)

GATE CSE 1996 (1)

GATE CSE 1995 (3)

GATE CSE Subjects

Theory of Computation

Operating Systems

Algorithms

Database Management System

Data Structures

Computer Networks

Software Engineering

Compiler Design

Web Technologies

General Aptitude

Discrete Mathematics

Programming Languages