1

GATE ECE 2003

MCQ (Single Correct Answer)

+1

-0.3

A 0 to 6 counter consist of 3 flip-flops and a combination circuit of 2 input gate(s). The combination circuit consists of

2

GATE ECE 2003

MCQ (Single Correct Answer)

+2

-0.6

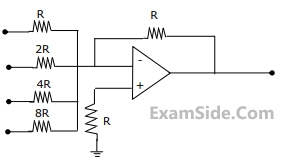

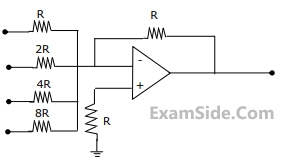

The circuit shown in figure is a 4-bit DAC

The input bits 0 and 1 are represented by 0 and 5 V respectively. The OP- AMP is ideal, but all the resistances and the 5V inputs have a tolerance of ±10%.

The input bits 0 and 1 are represented by 0 and 5 V respectively. The OP- AMP is ideal, but all the resistances and the 5V inputs have a tolerance of ±10%.

The specification (rounded to the nearest multiple of 5%) for the tolerance of the DAC is

The input bits 0 and 1 are represented by 0 and 5 V respectively. The OP- AMP is ideal, but all the resistances and the 5V inputs have a tolerance of ±10%.

The input bits 0 and 1 are represented by 0 and 5 V respectively. The OP- AMP is ideal, but all the resistances and the 5V inputs have a tolerance of ±10%.

The specification (rounded to the nearest multiple of 5%) for the tolerance of the DAC is

3

GATE ECE 2003

MCQ (Single Correct Answer)

+2

-0.6

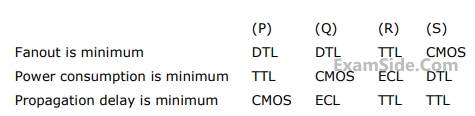

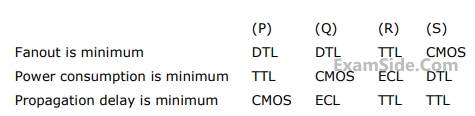

The DTL, TTL, ECL and CMOS families of digital ICs are compared in the following 4 columns

4

GATE ECE 2003

MCQ (Single Correct Answer)

+1

-0.3

The output of the 74 series of TTL gates is taken from a BJT in

Paper analysis

Total Questions

Analog Circuits

12

Communications

8

Control Systems

11

Digital Circuits

11

Electromagnetics

9

Electronic Devices and VLSI

8

Engineering Mathematics

1

Microprocessors

1

Network Theory

11

Signals and Systems

7

More papers of GATE ECE

GATE ECE 2025

GATE ECE 2024

GATE ECE 2023

GATE ECE 2022

GATE ECE 2021

GATE ECE 2019

GATE ECE 2018

GATE ECE 2017 Set 1

GATE ECE 2017 Set 2

GATE ECE 2016 Set 2

GATE ECE 2016 Set 1

GATE ECE 2016 Set 3

GATE ECE 2015 Set 2

GATE ECE 2015 Set 1

GATE ECE 2015 Set 3

GATE ECE 2014 Set 4

GATE ECE 2014 Set 3

GATE ECE 2014 Set 2

GATE ECE 2014 Set 1

GATE ECE 2013

GATE ECE 2012

GATE ECE 2011

GATE ECE 2010

GATE ECE 2009

GATE ECE 2008

GATE ECE 2007

GATE ECE 2006

GATE ECE 2005

GATE ECE 2004

GATE ECE 2003

GATE ECE 2002

GATE ECE 2001

GATE ECE 2000

GATE ECE 1999

GATE ECE 1998

GATE ECE 1997

GATE ECE 1996

GATE ECE 1995

GATE ECE 1994

GATE ECE 1993

GATE ECE 1992

GATE ECE 1991

GATE ECE 1990

GATE ECE 1989

GATE ECE 1988

GATE ECE 1987

GATE ECE

Papers

2025

2024

2023

2022

2021

2019

2018

2014

2013

2012

2011

2010

2009

2008

2007

2006

2005

2004

2003

2002

2001

2000

1999

1998

1997

1996

1995

1994

1993

1992

1991

1990

1989

1988

1987