1

GATE EE 2006

MCQ (Single Correct Answer)

+2

-0.6

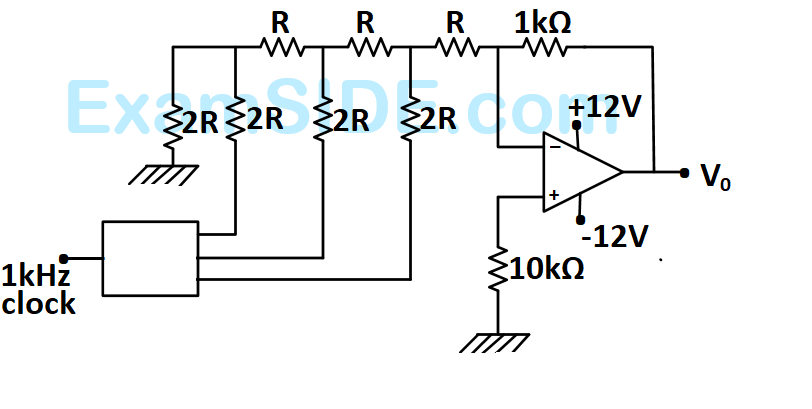

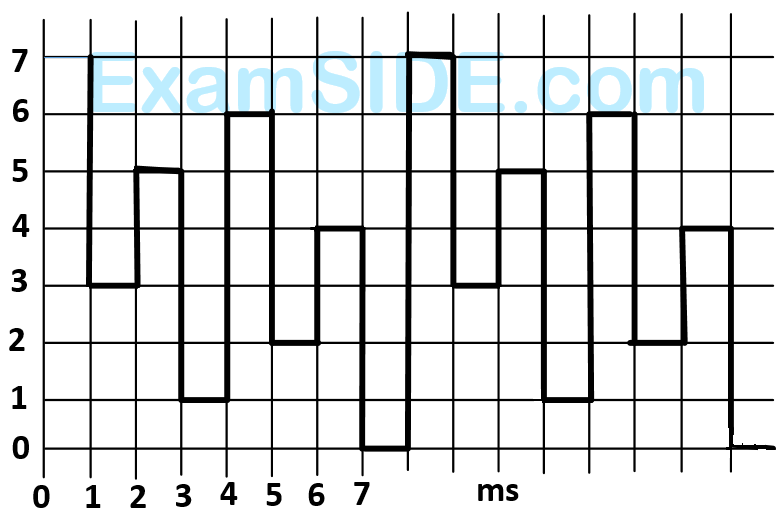

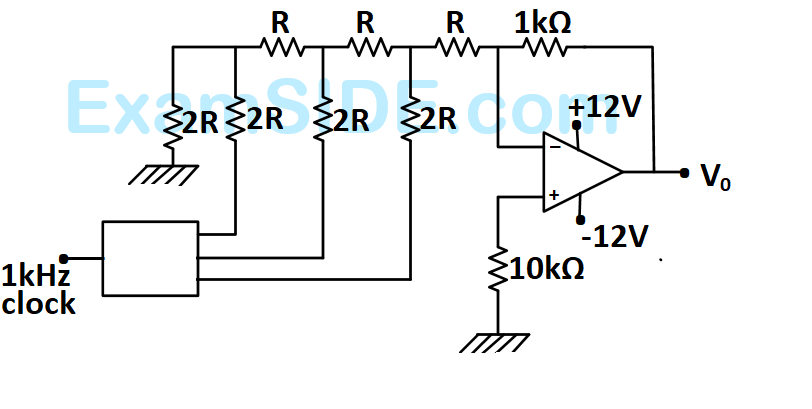

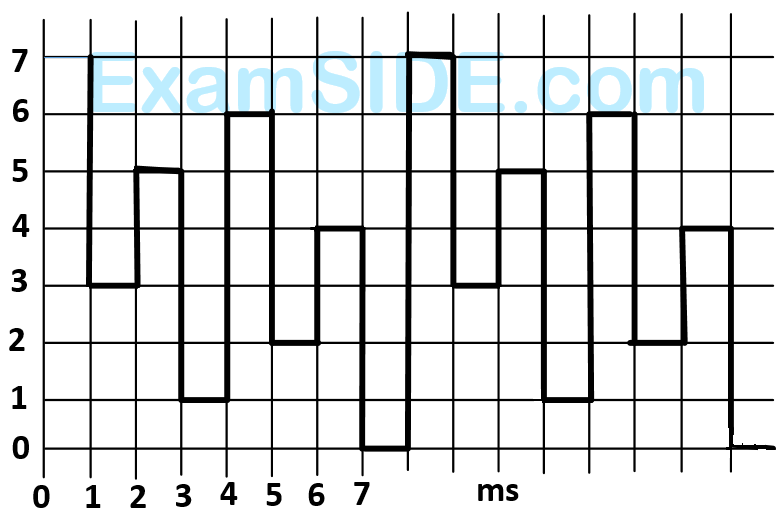

A student has made a-$$3$$ bit binary down counter and connected to the $$R$$-$$2R$$ ladder type $$DAC$$ [Gain $$=$$ $$\left( { - 1k\Omega /2R} \right)$$ as shown in figure to generate a staircase waveform.

The output achieved is different as shown in figure. What could be the possible cause of this error?

2

GATE EE 2005

MCQ (Single Correct Answer)

+2

-0.6

A digital-to-analog converter with a full -scale output voltage of $$3.5$$ $$V$$ has a resolution close to $$14$$ $$m$$ $$V.$$ Its bit size is

3

GATE EE 2003

MCQ (Single Correct Answer)

+2

-0.6

The simplified block diagram of a $$10$$-bit $$A/D$$ converter of dual slope integrator type is shown in Fig. The $$10$$-bit counter at the output is clocked by a $$1$$ $$MHz$$ clock. Assuming negligible timing overhead for the control logic, the maximum frequency of the analog signal that can be converted using this $$A/D$$ converter is approximately. Input sample to be converter

4

GATE EE 1999

MCQ (Single Correct Answer)

+2

-0.6

For a dual $$ADC$$ type $$3\,{\raise0.5ex\hbox{$\scriptstyle 1$}

\kern-0.1em/\kern-0.15em

\lower0.25ex\hbox{$\scriptstyle 2$}}$$ digit $$DVM$$, the reference voltage is $$100$$ $$mV$$ and the first integration time is set to $$300$$ $$ms$$. For some input voltage, the ''deintegration'' period is $$370.2ms.$$ The $$DVM$$ will indicate.

Questions Asked from Analog to Digital and Digital to Analog Converter (Marks 2)

Number in Brackets after Paper Indicates No. of Questions

GATE EE Subjects

Electric Circuits

Electromagnetic Fields

Signals and Systems

Electrical Machines

Engineering Mathematics

General Aptitude

Power System Analysis

Electrical and Electronics Measurement

Analog Electronics

Control Systems

Power Electronics