Marks 1

To obtain the Boolean function $F(X, Y) = X\overline{Y} + \overline{X}$, the inputs $PQRS$ in the figure should be

Marks 2

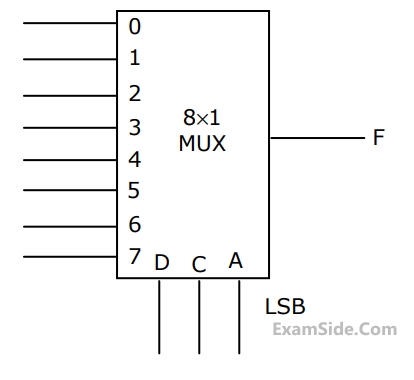

Which one of the following options gives the correct inputs to pins $$0,1,2,3,4,5,6,7$$ in order?

The monoshots $${{M_1}}$$ and $${{M_2}}$$ when triggered produce pulses of width $${{T_1}}$$ and $${{T_2}}$$ respectively, where $${T_1} > {T_2}.$$ The steady state output voltage $${V_0}$$ of the circuit is

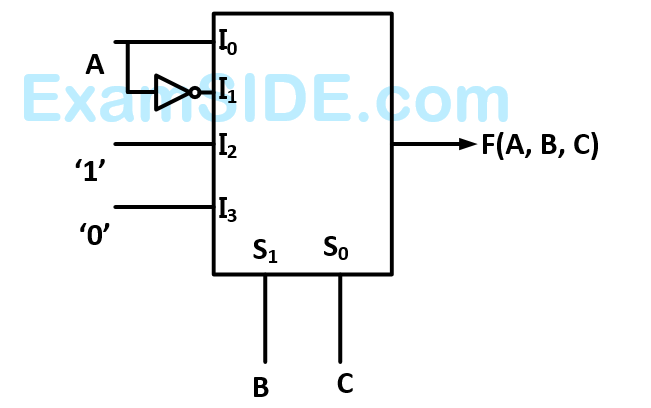

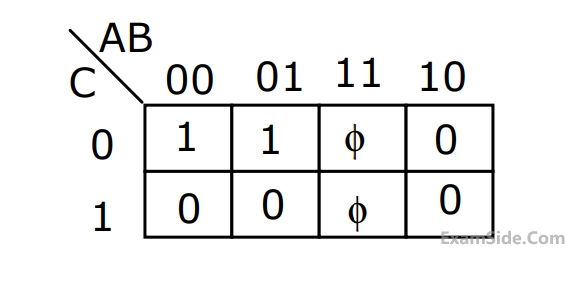

$$(a)$$ Indicate the inputs to be applied at the terminals $$0$$ to $$7.$$

$$(b)$$ Can the function be realize using a $$4$$ to $$1$$ multiplexer?

State YES or NO.

Marks 5

$$(A = 1; B = C = D = 0).$$ It is known that the following combinations of input are forbidden:

$$ABCD = 1010, 1011, 1100, 1101, 1110, 1111$$

Evaluate the logical expression for the output and realize the same with two input $$NAND$$ gates. Assume that

complements of inputs are not available.