1

GATE EE 2006

MCQ (Single Correct Answer)

+2

-0.6

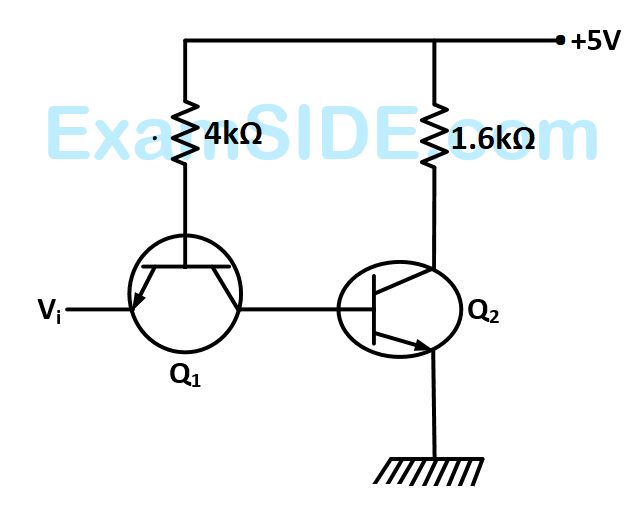

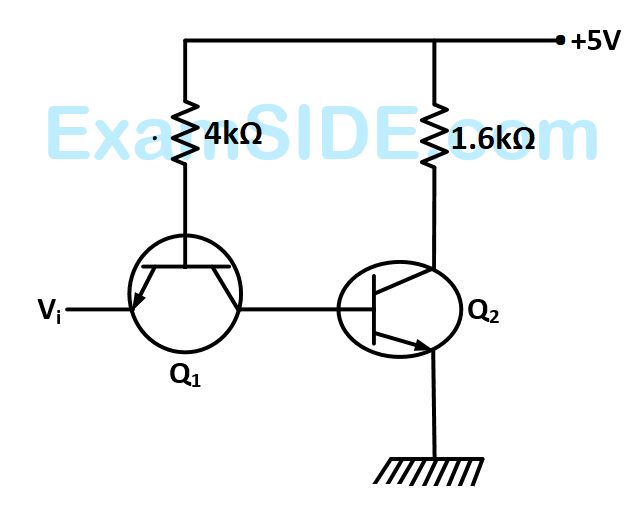

A TTL NOT gate circuit is shown in figure. Assuming $${V_{BE}} = 0.7\,v$$ of both the transistors, if $${V_i} = 3.0\,V,$$ then the states of the two transistors will be

Questions Asked from Logic Families and Memories (Marks 2)

Number in Brackets after Paper Indicates No. of Questions

GATE EE Subjects

Electric Circuits

Electromagnetic Fields

Signals and Systems

Electrical Machines

Engineering Mathematics

General Aptitude

Power System Analysis

Electrical and Electronics Measurement

Analog Electronics

Control Systems

Power Electronics