1

GATE ECE 1998

MCQ (Single Correct Answer)

+1

-0.3

An I/O processor control the flow of information between

2

GATE ECE 1998

Subjective

+5

-0

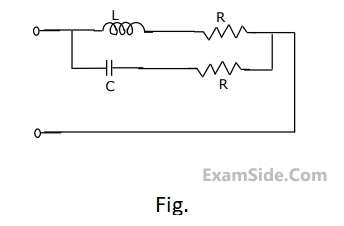

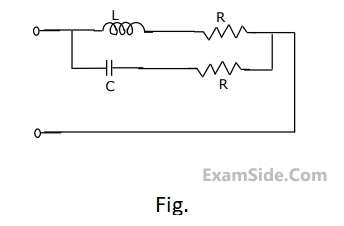

Determine the frequency of resonance and the resonant impedance of the parallel circuit shown in figure. What happens when $$L = C{R^2}$$?

3

GATE ECE 1998

MCQ (Single Correct Answer)

+1

-0.3

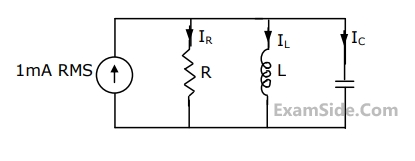

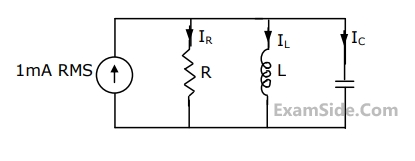

The parallel $$RLC$$ circuit shown in figure is in resonance. In this circuit

4

GATE ECE 1998

MCQ (Single Correct Answer)

+1

-0.3

A network has 7 nodes and 5 independent loops. The number of branches in the

network is

Paper analysis

Total Questions

Analog Circuits

13

Communications

9

Control Systems

14

Digital Circuits

10

Electromagnetics

16

Electronic Devices and VLSI

2

Engineering Mathematics

2

Microprocessors

2

Network Theory

8

Signals and Systems

11

More papers of GATE ECE

GATE ECE 2025

GATE ECE 2024

GATE ECE 2023

GATE ECE 2022

GATE ECE 2021

GATE ECE 2019

GATE ECE 2018

GATE ECE 2017 Set 1

GATE ECE 2017 Set 2

GATE ECE 2016 Set 2

GATE ECE 2016 Set 1

GATE ECE 2016 Set 3

GATE ECE 2015 Set 2

GATE ECE 2015 Set 1

GATE ECE 2015 Set 3

GATE ECE 2014 Set 4

GATE ECE 2014 Set 3

GATE ECE 2014 Set 2

GATE ECE 2014 Set 1

GATE ECE 2013

GATE ECE 2012

GATE ECE 2011

GATE ECE 2010

GATE ECE 2009

GATE ECE 2008

GATE ECE 2007

GATE ECE 2006

GATE ECE 2005

GATE ECE 2004

GATE ECE 2003

GATE ECE 2002

GATE ECE 2001

GATE ECE 2000

GATE ECE 1999

GATE ECE 1998

GATE ECE 1997

GATE ECE 1996

GATE ECE 1995

GATE ECE 1994

GATE ECE 1993

GATE ECE 1992

GATE ECE 1991

GATE ECE 1990

GATE ECE 1989

GATE ECE 1988

GATE ECE 1987

GATE ECE

Papers

2025

2024

2023

2022

2021

2019

2018

2014

2013

2012

2011

2010

2009

2008

2007

2006

2005

2004

2003

2002

2001

2000

1999

1998

1997

1996

1995

1994

1993

1992

1991

1990

1989

1988

1987