1

MHT CET 2025 25th April Morning Shift

MCQ (Single Correct Answer)

+1

-0

The logic gate for which the output goes 'HIGH' or ' 1 ' only when an odd number of 'HIGH' or ' 1 ' are at its input, is

2

MHT CET 2025 25th April Morning Shift

MCQ (Single Correct Answer)

+1

-0

To get output of the following logic circuit as ' 0 ' (zero), the inputs $A, B, C$ should NOT be, respectively,

3

MHT CET 2025 25th April Morning Shift

MCQ (Single Correct Answer)

+1

-0

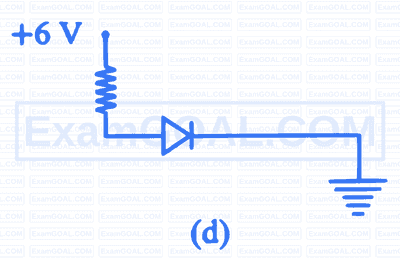

In which of the following figures, the p.n. junction diode is reverse biased?

4

MHT CET 2025 23rd April Evening Shift

MCQ (Single Correct Answer)

+1

-0

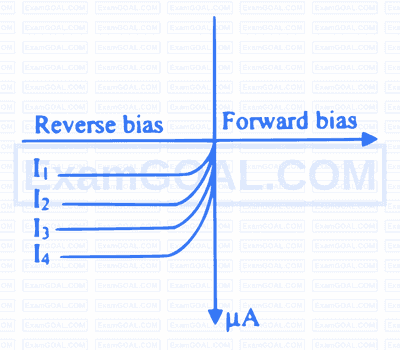

I - V characteristics of photodiode for different illumination intensities $\mathrm{I}_1, \mathrm{I}_2, \mathrm{I}_3$ and $\mathrm{I}_4$ are drawn as follows. Then the maximum intensity among them is

Questions Asked from Semiconductor Devices and Logic Gates (MCQ (Single Correct Answer))

Number in Brackets after Paper Indicates No. of Questions

MHT CET 2025 25th April Morning Shift (3)

MHT CET 2025 23rd April Evening Shift (3)

MHT CET 2025 23rd April Morning Shift (3)

MHT CET 2025 22nd April Evening Shift (3)

MHT CET 2025 22nd April Morning Shift (4)

MHT CET 2025 21st April Evening Shift (3)

MHT CET 2025 21st April Morning Shift (3)

MHT CET 2025 20th April Evening Shift (3)

MHT CET 2025 20th April Morning Shift (3)

MHT CET 2025 19th April Evening Shift (3)

MHT CET 2025 19th April Morning Shift (3)

MHT CET 2024 16th May Evening Shift (3)

MHT CET 2024 16th May Morning Shift (3)

MHT CET 2024 15th May Evening Shift (3)

MHT CET 2024 15th May Morning Shift (3)

MHT CET 2024 11th May Evening Shift (3)

MHT CET 2024 11th May Morning Shift (3)

MHT CET 2024 10th May Evening Shift (3)

MHT CET 2024 10th May Morning Shift (3)

MHT CET 2024 9th May Evening Shift (2)

MHT CET 2024 9th May Morning Shift (3)

MHT CET 2024 4th May Evening Shift (3)

MHT CET 2024 4th May Morning Shift (3)

MHT CET 2024 3rd May Evening Shift (3)

MHT CET 2024 3rd May Morning Shift (3)

MHT CET 2024 2nd May Evening Shift (2)

MHT CET 2024 2nd May Morning Shift (3)

MHT CET 2023 14th May Evening Shift (3)

MHT CET 2023 14th May Morning Shift (3)

MHT CET 2023 13th May Evening Shift (3)

MHT CET 2023 13th May Morning Shift (3)

MHT CET 2023 12th May Evening Shift (3)

MHT CET 2023 12th May Morning Shift (3)

MHT CET 2023 11th May Evening Shift (3)

MHT CET 2023 11th May Morning Shift (3)

MHT CET 2023 10th May Evening Shift (4)

MHT CET 2023 10th May Morning Shift (3)

MHT CET 2023 9th May Evening Shift (3)

MHT CET 2023 9th May Morning Shift (3)

MHT CET 2022 11th August Evening Shift (2)

MHT CET 2021 24th September Evening Shift (3)

MHT CET 2021 24th September Morning Shift (3)

MHT CET 2021 23rd September Evening Shift (3)

MHT CET 2021 23th September Morning Shift (3)

MHT CET 2021 22th September Evening Shift (3)

MHT CET 2021 22th September Morning Shift (3)

MHT CET 2021 21th September Evening Shift (3)

MHT CET 2021 21th September Morning Shift (3)

MHT CET 2021 20th September Evening Shift (3)

MHT CET 2021 20th September Morning Shift (3)

MHT CET 2020 19th October Evening Shift (2)

MHT CET 2020 16th October Evening Shift (2)

MHT CET 2020 16th October Morning Shift (2)

MHT CET 2019 3rd May Morning Shift (2)

MHT CET 2019 2nd May Evening Shift (2)

MHT CET 2019 2nd May Morning Shift (2)

MHT CET Subjects

Physics

Mechanics

Units & Measurement and Dimensions Vector Algebra Motion Laws of Motion Circular Motion Work, Energy and Power Center of Mass and Collision Rotational Motion Gravitation Simple Harmonic Motion Fluid Mechanics Elasticity Waves Heat and Thermodynamics

Optics

Electromagnetism

Electrostatics Current Electricity Capacitor Moving Charges and Magnetism Magnetism and Matter Electromagnetic Waves Electromagnetic Induction Alternating Current

Modern Physics

Chemistry

Physical Chemistry

Some Basic Concepts of Chemistry Atomic Structure States of Matter Thermodynamics Chemical Equilibrium Ionic Equilibrium Liquid Solution Redox Reactions Surface Chemistry Solid State Electrochemistry Chemical Kinetics Nuclear Chemistry

Inorganic Chemistry

Periodic Table and Periodicity Chemical Bonding and Molecular Structure Metallurgy Hydrogen and It's Compounds s-Block Elements p-Block Elements d and f Block Elements Coordination Compounds Environmental Chemistry

Organic Chemistry

Mathematics

Algebra

Sets and Relations Logarithms Quadratic Equations Sequences and Series Binomial Theorem Permutations and Combinations Probability Vector Algebra Three Dimensional Geometry Matrices and Determinants Statistics Mathematical Reasoning Linear Programming Complex Numbers

Trigonometry

Trigonometric Ratios & Identities Trigonometric Equations Inverse Trigonometric Functions Properties of Triangles

Calculus

Functions Limits, Continuity and Differentiability Differentiation Application of Derivatives Indefinite Integration Definite Integration Area Under The Curves Differential Equations

Coordinate Geometry