| Process | Arrival Time | Time Units Required |

|---|---|---|

| P1 | 0 | 5 |

| P2 | 1 | 7 |

| P3 | 3 | 4 |

The completion order of the $$3$$ processes under the policies $$FCFS$$ and $$RR2$$ (round robin scheduling with $$CPU$$ quantum of $$2$$ time units) are

| Process | Arrival Time | Burst Time |

|---|---|---|

| P0 | 0 ms | 9 ms |

| P1 | 1 ms | 4 ms |

| P2 | 2 ms | 9 ms |

The pre-emptive shortest job first scheduling algorithm is used. Scheduling is carried out only a arrival or completion of processes. What is the average waiting time for the three processes?

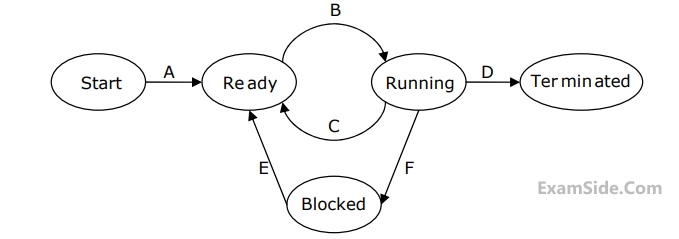

Now consider the following statements:

$$1.\,\,\,$$ If a process makes a transition $$D,$$ it would result in another process making transition $$A$$ immediately.

$$2.\,\,\,$$ $$A$$ process $${P_2}$$ in blocked state can make transition $$E$$ while another process $${P_1}$$ is in running state.

$$3.\,\,\,$$ The $$OS$$ uses preemptive scheduling.

$$4.\,\,\,$$ The $$OS$$ uses non-preemptive scheduling.

Which of the above statements are TRUE?

$${\rm I}.\,\,\,$$ It is useful in creating self-relocating code

$${\rm II}.\,\,\,$$ If it is included in an Instruction Set Architecture, then an additional $$ALU$$ is required for effective address calculation.

$${\rm III}.\,\,\,$$ The amount of increment depends on the size of the data item accessed