The first operand (destination) ''$$A$$ $$\left[ {{R_0}} \right]''$$ uses indexed addressing mode with $${{R_0}}$$ as the index register. The second operand (source) $$''@B''$$ used indirect addressing mode. $$A$$ and $$B$$ are memory addresses residing at the second and the third words, respectively. The first word of the instruction specific the opcode, the index register designation and the source and destination addressing modes. During execution of $$ADD$$ instruction, the two operands are added and stored in the destination (first operand).

The number of memory cycles needed during the execution cycle of the instruction is

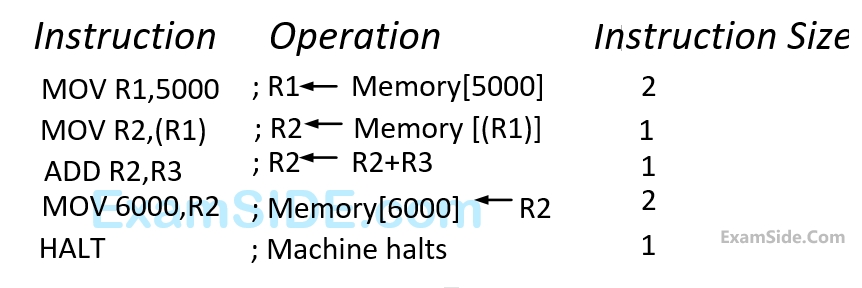

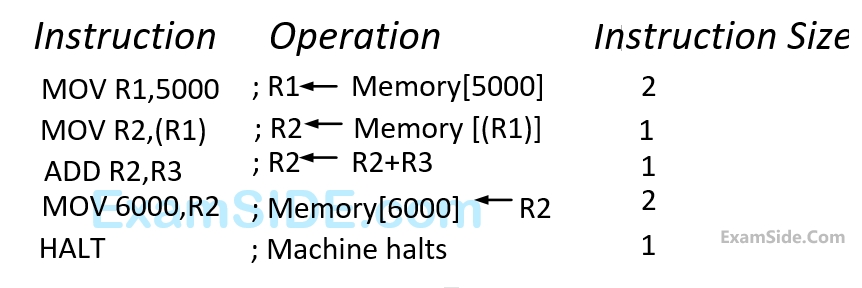

Consider that the memory is byte addressable with word size $$32$$ bits, and the program has been loaded starting from memory location $$1000$$ (decimal). If an interrupt occurs while the $$CPU$$ has been halted after executing the HALT instruction, the return address (in decimal) saved in the stack will be

Let the clock cycles required for various operations be as follows:

Register to/from memory transfer:

$$3$$ clock cycles

ADD with both operands in register:

$$1$$ clock cycle

Instruction fetch and decode:

$$2$$ clock cycles per word

The total number of clock cycle required to execute the program is

$$X.$$ Indirect Addressing

$$Y.$$ Indexed Addressing

$$Z.$$ Base Register Addressing

$${\rm I}.\,\,$$Array implementation

$${\rm II}.\,\,$$Writing relocatable code

$${\rm III}.\,\,$$Passing array as parameter