1

GATE ECE 2017 Set 1

MCQ (Single Correct Answer)

+2

-0.6

The Nyquist plot of the transfer function

$$G(s) = {k \over {\left( {{s^2} + 2s + 2} \right)\left( {s + 2} \right)}}$$

does not encircle the point (-1+j0) for K = 10 but does encircle the point (-1+j0) for K = 100. Then the closed loop system (having unity gain feedback) is

2

GATE ECE 2017 Set 1

MCQ (Single Correct Answer)

+1

-0.3

Which of the following can be the pole-zero configuration of a phase-lag controller (lag compensator)?

3

GATE ECE 2017 Set 1

MCQ (Single Correct Answer)

+2

-0.6

Which one of the following gives the simplified sum of products expression for the Boolean function $$F = {m_0} + {m_2} + {m_3} + {m_5},$$ where $$F = {m_0} + {m_2} + {m_3} + {m_5},$$ are minterms corresponding to the inputs A, B

and C with A as the MSB and C as the LSB?

4

GATE ECE 2017 Set 1

Numerical

+1

-0

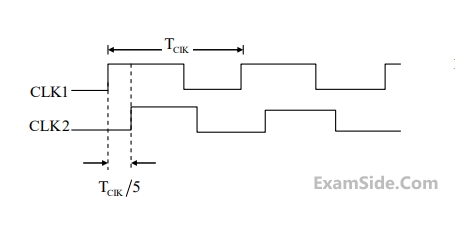

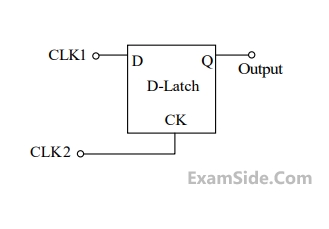

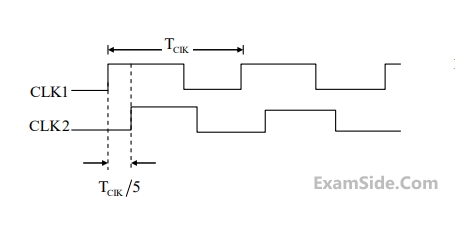

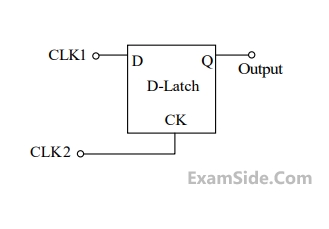

Consider the D-Latch shown in the figure, which is transparent when its clock input CK is high and has zero propagation delay. In the figure, the clock signal CLK1 has a 50% duty cycle and CLK2 is a one-fifth period delayed version of CLK1. The duty cycle at the output latch in percentage is ___________.

Your input ____

Paper analysis

Total Questions

Analog Circuits

5

Communications

5

Control Systems

6

Digital Circuits

5

Electromagnetics

5

Electronic Devices and VLSI

4

Engineering Mathematics

10

Microprocessors

2

Network Theory

3

Signals and Systems

7

General Aptitude

10

More papers of GATE ECE

GATE ECE 2025

GATE ECE 2024

GATE ECE 2023

GATE ECE 2022

GATE ECE 2021

GATE ECE 2019

GATE ECE 2018

GATE ECE 2017 Set 1

GATE ECE 2017 Set 2

GATE ECE 2016 Set 2

GATE ECE 2016 Set 1

GATE ECE 2016 Set 3

GATE ECE 2015 Set 2

GATE ECE 2015 Set 1

GATE ECE 2015 Set 3

GATE ECE 2014 Set 4

GATE ECE 2014 Set 3

GATE ECE 2014 Set 2

GATE ECE 2014 Set 1

GATE ECE 2013

GATE ECE 2012

GATE ECE 2011

GATE ECE 2010

GATE ECE 2009

GATE ECE 2008

GATE ECE 2007

GATE ECE 2006

GATE ECE 2005

GATE ECE 2004

GATE ECE 2003

GATE ECE 2002

GATE ECE 2001

GATE ECE 2000

GATE ECE 1999

GATE ECE 1998

GATE ECE 1997

GATE ECE 1996

GATE ECE 1995

GATE ECE 1994

GATE ECE 1993

GATE ECE 1992

GATE ECE 1991

GATE ECE 1990

GATE ECE 1989

GATE ECE 1988

GATE ECE 1987

GATE ECE

Papers

2025

2024

2023

2022

2021

2019

2018

2014

2013

2012

2011

2010

2009

2008

2007

2006

2005

2004

2003

2002

2001

2000

1999

1998

1997

1996

1995

1994

1993

1992

1991

1990

1989

1988

1987