1

GATE ECE 2016 Set 2

Numerical

+2

-0

In the feedback system shown below

$${\rm{G(s) = }}{1 \over {\left( {s + 1} \right)\left( {s + 2} \right)\left( {s + 3} \right)}}$$

The positive value of 𝑘 for which the gain margin of the loop is exactly 0 dB and the phase margin

of the loop is exactly zero degree is ____

The positive value of 𝑘 for which the gain margin of the loop is exactly 0 dB and the phase margin

of the loop is exactly zero degree is ____

The positive value of 𝑘 for which the gain margin of the loop is exactly 0 dB and the phase margin

of the loop is exactly zero degree is ____

The positive value of 𝑘 for which the gain margin of the loop is exactly 0 dB and the phase margin

of the loop is exactly zero degree is ____Your input ____

2

GATE ECE 2016 Set 2

Numerical

+2

-0

The asymptotic Bode phase plot of

$${\rm{G(s) = }}{k \over {\left( {s + 0.1} \right)\left( {s + 10} \right)\left( {s + {p_1}} \right)}},$$

with k and p1 both positive, is shown below.

The value of p1 is ________

The value of p1 is ________

The value of p1 is ________

The value of p1 is ________Your input ____

3

GATE ECE 2016 Set 2

Numerical

+1

-0

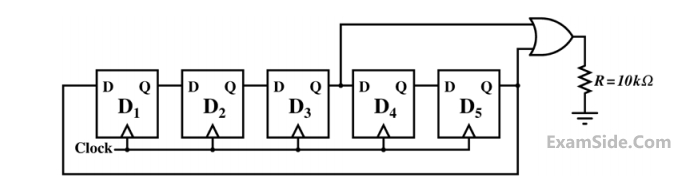

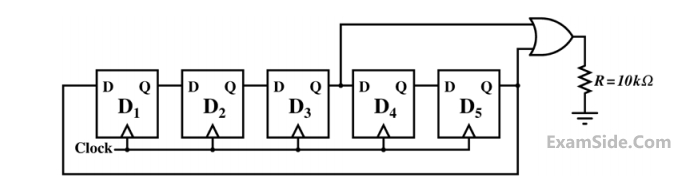

Assume that all the digital gates in the circuit shown in the figure are ideal, the resistor 𝑅 = 10 𝑘Ω and the supply voltage is 5 𝑉. The D flip-flops D1, D2, D3, D4 and D5 are initialized with logic

values 0, 1, 0,1 and 0, respectively. The clock has a 30% duty cycle.

The average power dissipated (in mW) in resistor R is ______.

Your input ____

4

GATE ECE 2016 Set 2

MCQ (Single Correct Answer)

+2

-0.6

The state transition diagram for a finite state machine with states A, B and C, and binary inputs X, Y and Z, is shown in the figure.

Which one of the following statements is correct?

Paper analysis

Total Questions

Analog Circuits

6

Communications

6

Control Systems

5

Digital Circuits

5

Electromagnetics

7

Electronic Devices and VLSI

6

Engineering Mathematics

7

Microprocessors

1

Network Theory

6

Signals and Systems

3

General Aptitude

2

More papers of GATE ECE

GATE ECE 2025

GATE ECE 2024

GATE ECE 2023

GATE ECE 2022

GATE ECE 2021

GATE ECE 2019

GATE ECE 2018

GATE ECE 2017 Set 1

GATE ECE 2017 Set 2

GATE ECE 2016 Set 2

GATE ECE 2016 Set 1

GATE ECE 2016 Set 3

GATE ECE 2015 Set 2

GATE ECE 2015 Set 1

GATE ECE 2015 Set 3

GATE ECE 2014 Set 4

GATE ECE 2014 Set 3

GATE ECE 2014 Set 2

GATE ECE 2014 Set 1

GATE ECE 2013

GATE ECE 2012

GATE ECE 2011

GATE ECE 2010

GATE ECE 2009

GATE ECE 2008

GATE ECE 2007

GATE ECE 2006

GATE ECE 2005

GATE ECE 2004

GATE ECE 2003

GATE ECE 2002

GATE ECE 2001

GATE ECE 2000

GATE ECE 1999

GATE ECE 1998

GATE ECE 1997

GATE ECE 1996

GATE ECE 1995

GATE ECE 1994

GATE ECE 1993

GATE ECE 1992

GATE ECE 1991

GATE ECE 1990

GATE ECE 1989

GATE ECE 1988

GATE ECE 1987

GATE ECE

Papers

2025

2024

2023

2022

2021

2019

2018

2014

2013

2012

2011

2010

2009

2008

2007

2006

2005

2004

2003

2002

2001

2000

1999

1998

1997

1996

1995

1994

1993

1992

1991

1990

1989

1988

1987