1

GATE ECE 2016 Set 2

MCQ (Single Correct Answer)

+2

-0.6

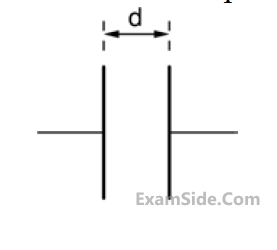

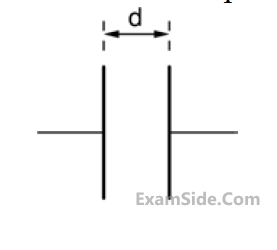

The parallel-plate capacitor shown in the figure has movable plates. The capacitor is charged

so that the energy stored in it is E when the plate separation is d. The capacitor is then isolated

electrically and the plates are moved such that the plate separation becomes 2d.

At this new plate separation, what is the energy stored in the capacitor, neglecting fringing effects?

2

GATE ECE 2016 Set 2

Numerical

+2

-0

Consider a region of silicon devoid of electrons and holes, with an ionized donor density of

$${\mathrm N}_\mathrm d^+=10^{17}\;\mathrm{cm}^{-3}$$. The electric field at x = 0 is 0 V/cm and the electric field at x = L is

50 kV/cm in the positive x direction. Assume that the electric field is zero in the y and z directions

at all points.

Given q = 1.6 × 10−19 coulomb, $$\varepsilon$$0 = 8.85 × 10−14 F/cm, $$\varepsilon$$r = 11.7 for silicon, the value of L in nm is ________.

Your input ____

3

GATE ECE 2016 Set 2

MCQ (Single Correct Answer)

+1

-0.3

The Ebers-Moll model of a BJT is valid

4

GATE ECE 2016 Set 2

MCQ (Single Correct Answer)

+1

-0.3

A long-channel NMOS transistor is biased in the linear region with VDS = 50 mV and is used

as a resistance. Which one of the following statements is NOT correct?

Paper analysis

Total Questions

Analog Circuits

6

Communications

6

Control Systems

5

Digital Circuits

5

Electromagnetics

7

Electronic Devices and VLSI

6

Engineering Mathematics

7

Microprocessors

1

Network Theory

6

Signals and Systems

3

General Aptitude

2

More papers of GATE ECE

GATE ECE 2025

GATE ECE 2024

GATE ECE 2023

GATE ECE 2022

GATE ECE 2021

GATE ECE 2019

GATE ECE 2018

GATE ECE 2017 Set 2

GATE ECE 2017 Set 1

GATE ECE 2016 Set 3

GATE ECE 2016 Set 2

GATE ECE 2016 Set 1

GATE ECE 2015 Set 2

GATE ECE 2015 Set 3

GATE ECE 2015 Set 1

GATE ECE 2014 Set 1

GATE ECE 2014 Set 4

GATE ECE 2014 Set 3

GATE ECE 2014 Set 2

GATE ECE 2013

GATE ECE 2012

GATE ECE 2011

GATE ECE 2010

GATE ECE 2009

GATE ECE 2008

GATE ECE 2007

GATE ECE 2006

GATE ECE 2005

GATE ECE 2004

GATE ECE 2003

GATE ECE 2002

GATE ECE 2001

GATE ECE 2000

GATE ECE 1999

GATE ECE 1998

GATE ECE 1997

GATE ECE 1996

GATE ECE 1995

GATE ECE 1994

GATE ECE 1993

GATE ECE 1992

GATE ECE 1991

GATE ECE 1990

GATE ECE 1989

GATE ECE 1988

GATE ECE 1987

GATE ECE

Papers

2025

2024

2023

2022

2021

2019

2018

2014

2013

2012

2011

2010

2009

2008

2007

2006

2005

2004

2003

2002

2001

2000

1999

1998

1997

1996

1995

1994

1993

1992

1991

1990

1989

1988

1987