1

GATE ECE 2002

Subjective

+5

-0

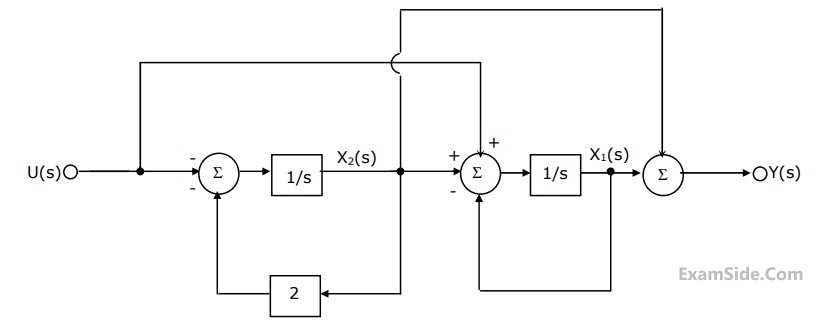

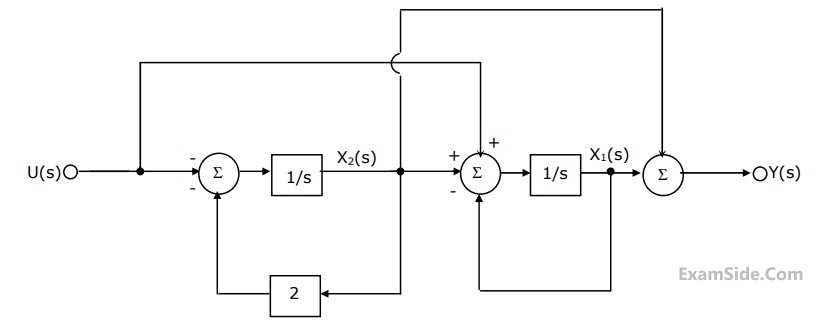

The block diagram of a linear time invariant system is given in Figure is

(a) Write down the state variable equations for the system in matrix form

assuming the state vector to be $${\left[ {{x_1}\left( t \right)\,\,{x_2}\left( t \right)} \right]^T}$$

(a) Write down the state variable equations for the system in matrix form

assuming the state vector to be $${\left[ {{x_1}\left( t \right)\,\,{x_2}\left( t \right)} \right]^T}$$

(b) Find out the state transition matrix.

(c) Determine y(t), t ≥ 0, when the initial values of the state at time t = 0 are $${x_1}$$(0) = 1, and $${x_2}$$(0) = 1.

(a) Write down the state variable equations for the system in matrix form

assuming the state vector to be $${\left[ {{x_1}\left( t \right)\,\,{x_2}\left( t \right)} \right]^T}$$

(a) Write down the state variable equations for the system in matrix form

assuming the state vector to be $${\left[ {{x_1}\left( t \right)\,\,{x_2}\left( t \right)} \right]^T}$$

(b) Find out the state transition matrix.

(c) Determine y(t), t ≥ 0, when the initial values of the state at time t = 0 are $${x_1}$$(0) = 1, and $${x_2}$$(0) = 1.

2

GATE ECE 2002

MCQ (Single Correct Answer)

+1

-0.3

The number of comparators required in a 3-bit comparator type ADC is

3

GATE ECE 2002

Subjective

+5

-0

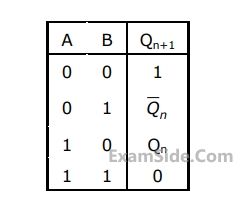

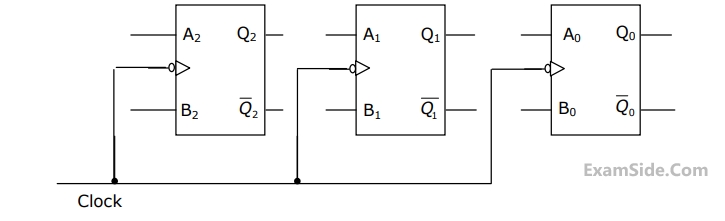

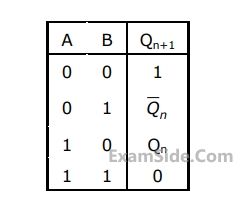

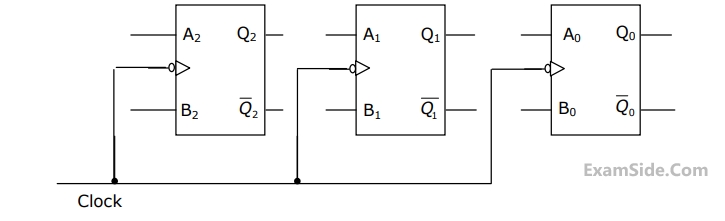

It is required to design a binary mod-5 synchronus counter using AB flip-flops such that the output Q2Q1Q0 changes as $$000 \to 001 \to 010$$ ........and so on. The excitation table for the AB flip-flops is given in the table

(a) Write down the state table for the mod-5 counter.

(b)Obtain simplified SOP expressions for the inputs A2, B2, A1, B1, A0 and B0 in terms of Q2, Q1, Q and their complements.

(c) Hence, complete the circuit diagram for the mod-5 counter given in the figure using minimum number of 2-input NAND-gate only.

4

GATE ECE 2002

MCQ (Single Correct Answer)

+2

-0.6

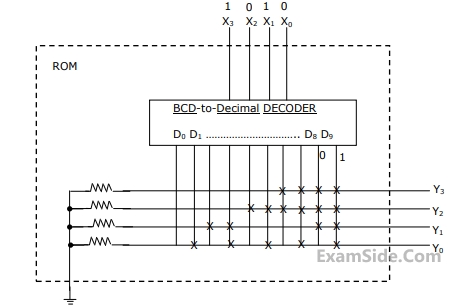

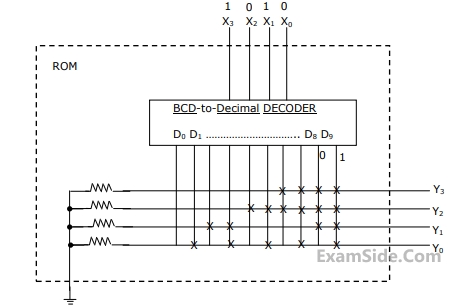

If the input X$$_3$$, X$$_2$$, X$$_1$$, X$$_0$$ to the ROM in figure 2.12 are 8-4-2-1 BCD numbers, then the outpus are Y$$_3$$,Y$$_2$$, Y$$_1$$, Y$$_0$$ are

Paper analysis

Total Questions

Analog Circuits

4

Communications

3

Control Systems

11

Digital Circuits

7

Electromagnetics

11

Electronic Devices and VLSI

4

Microprocessors

2

Network Theory

8

Signals and Systems

10

More papers of GATE ECE

GATE ECE 2025

GATE ECE 2024

GATE ECE 2023

GATE ECE 2022

GATE ECE 2021

GATE ECE 2019

GATE ECE 2018

GATE ECE 2017 Set 1

GATE ECE 2017 Set 2

GATE ECE 2016 Set 2

GATE ECE 2016 Set 1

GATE ECE 2016 Set 3

GATE ECE 2015 Set 2

GATE ECE 2015 Set 1

GATE ECE 2015 Set 3

GATE ECE 2014 Set 4

GATE ECE 2014 Set 3

GATE ECE 2014 Set 2

GATE ECE 2014 Set 1

GATE ECE 2013

GATE ECE 2012

GATE ECE 2011

GATE ECE 2010

GATE ECE 2009

GATE ECE 2008

GATE ECE 2007

GATE ECE 2006

GATE ECE 2005

GATE ECE 2004

GATE ECE 2003

GATE ECE 2002

GATE ECE 2001

GATE ECE 2000

GATE ECE 1999

GATE ECE 1998

GATE ECE 1997

GATE ECE 1996

GATE ECE 1995

GATE ECE 1994

GATE ECE 1993

GATE ECE 1992

GATE ECE 1991

GATE ECE 1990

GATE ECE 1989

GATE ECE 1988

GATE ECE 1987

GATE ECE

Papers

2025

2024

2023

2022

2021

2019

2018

2014

2013

2012

2011

2010

2009

2008

2007

2006

2005

2004

2003

2002

2001

2000

1999

1998

1997

1996

1995

1994

1993

1992

1991

1990

1989

1988

1987