1

GATE EE 2007

MCQ (Single Correct Answer)

+2

-0.6

$$R-L-C$$ circuit shown in figure

For a step input $${e_{i,}}$$ the overshoot in the output $${e_{0,}}$$ will be

2

GATE EE 2007

MCQ (Single Correct Answer)

+2

-0.6

$$R-L-C$$ circuit shown in figure

If the above step response is to be observed on a non - storage $$CRO,$$ then it would be best have the $${e_i}$$ as a

3

GATE EE 2005

MCQ (Single Correct Answer)

+2

-0.6

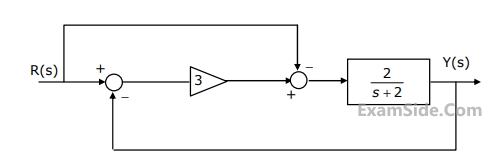

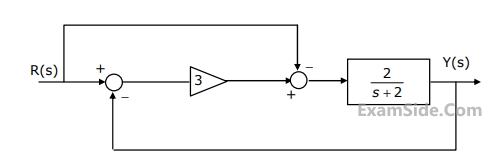

When subjected to a unit step input, the closed loop control system shown in the figure will have a steady state error of

4

GATE EE 2005

MCQ (Single Correct Answer)

+2

-0.6

When subjected to a unit step input, the closed loop control system shown in the figure will have a steady state error of

Questions Asked from Time Response Analysis (Marks 2)

Number in Brackets after Paper Indicates No. of Questions

GATE EE Subjects

Electromagnetic Fields

Signals and Systems

Engineering Mathematics

General Aptitude

Power Electronics

Power System Analysis

Analog Electronics

Control Systems

Digital Electronics

Electrical Machines

Electric Circuits