1

GATE ECE 2014 Set 3

MCQ (Single Correct Answer)

+2

-0.6

If X and Y are inputs and the Difference (D = X – Y) and the Borrow (B) are the outputs, which one of the following diagrams

implements a half-subtractor?

2

GATE ECE 2014 Set 3

MCQ (Single Correct Answer)

+1

-0.3

The circuit shown in the figure is a

3

GATE ECE 2014 Set 3

MCQ (Single Correct Answer)

+1

-0.3

Consider the multiplexer based logic circuit shown in the figure.

Which one of the following Boolean functions is realized by the circuit?

4

GATE ECE 2014 Set 3

MCQ (Single Correct Answer)

+1

-0.3

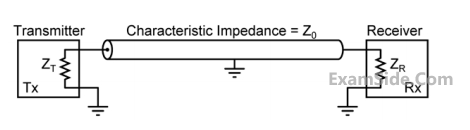

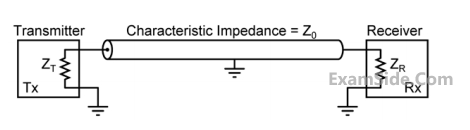

In the following figure, the transmitter Tx sends a wideband modulated RF signal via a coaxial cable to the receiver Rx. The output impedance $${Z_T}$$ of Tx, the characteristic impedance $${Z_0}$$ of the cable and the input impedance $${Z_R}$$ of Rx are all real.

Which one of the following statements is TRUE about the distortion of the received signal due to impedance mismatch?

Which one of the following statements is TRUE about the distortion of the received signal due to impedance mismatch?

Which one of the following statements is TRUE about the distortion of the received signal due to impedance mismatch?

Which one of the following statements is TRUE about the distortion of the received signal due to impedance mismatch?Paper analysis

Total Questions

Analog Circuits

5

Communications

6

Control Systems

5

Digital Circuits

5

Electromagnetics

5

Electronic Devices and VLSI

6

Engineering Mathematics

9

Network Theory

6

Signals and Systems

8

More papers of GATE ECE

GATE ECE 2025

GATE ECE 2024

GATE ECE 2023

GATE ECE 2022

GATE ECE 2021

GATE ECE 2019

GATE ECE 2018

GATE ECE 2017 Set 1

GATE ECE 2017 Set 2

GATE ECE 2016 Set 2

GATE ECE 2016 Set 1

GATE ECE 2016 Set 3

GATE ECE 2015 Set 2

GATE ECE 2015 Set 1

GATE ECE 2015 Set 3

GATE ECE 2014 Set 4

GATE ECE 2014 Set 3

GATE ECE 2014 Set 2

GATE ECE 2014 Set 1

GATE ECE 2013

GATE ECE 2012

GATE ECE 2011

GATE ECE 2010

GATE ECE 2009

GATE ECE 2008

GATE ECE 2007

GATE ECE 2006

GATE ECE 2005

GATE ECE 2004

GATE ECE 2003

GATE ECE 2002

GATE ECE 2001

GATE ECE 2000

GATE ECE 1999

GATE ECE 1998

GATE ECE 1997

GATE ECE 1996

GATE ECE 1995

GATE ECE 1994

GATE ECE 1993

GATE ECE 1992

GATE ECE 1991

GATE ECE 1990

GATE ECE 1989

GATE ECE 1988

GATE ECE 1987

GATE ECE

Papers

2025

2024

2023

2022

2021

2019

2018

2014

2013

2012

2011

2010

2009

2008

2007

2006

2005

2004

2003

2002

2001

2000

1999

1998

1997

1996

1995

1994

1993

1992

1991

1990

1989

1988

1987