1

GATE CSE 2001

Subjective

+5

-0

A $$CPU$$ has $$32$$-bit memory address and a $$256$$ $$KB$$ cache memory. The cache is organized as a $$4$$-way set associative cache with cache block size of $$16$$ bytes.

(a)$$\,\,\,\,$$ What is the number of sets in the cache?

(b)$$\,\,\,\,$$ What is the size (in bits) of the tag field per cache block?

(c)$$\,\,\,\,$$ What is the number and size of comparators required for tag matching?

(d)$$\,\,\,\,$$ How many address bits are required to find the byte offset within a cache block?

(e)$$\,\,\,\,$$ What is the total amount of extra memory (in bytes) required for the tag bits?

2

GATE CSE 1996

Subjective

+5

-0

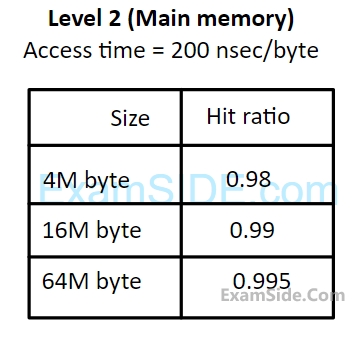

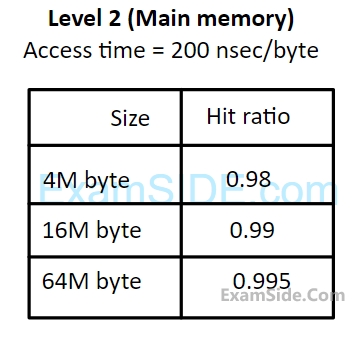

A computer system has a three level memory hierarchy, with access time and hit ratios as shown below:

(i) What should be the minimum size of level $$1$$ and $$2$$ memories to achieve an average access time of less than $$100$$ nsec?

(ii) What is the average access time achieved using the chosen sizes of level $$1$$ and level $$2$$ memories?

Questions Asked from Memory Interfacing (Marks 5)

Number in Brackets after Paper Indicates No. of Questions

GATE CSE Subjects

Theory of Computation

Operating Systems

Algorithms

Database Management System

Data Structures

Computer Networks

Software Engineering

Compiler Design

Web Technologies

General Aptitude

Discrete Mathematics

Programming Languages