1

GATE EE 2002

MCQ (Single Correct Answer)

+2

-0.6

For the circuit shown in Fig. the Boolean expression for the output $$Y$$ in terms of inputs $$P,$$ $$Q,$$ $$R$$ and $$S$$ is

2

GATE EE 2002

Subjective

+5

-0

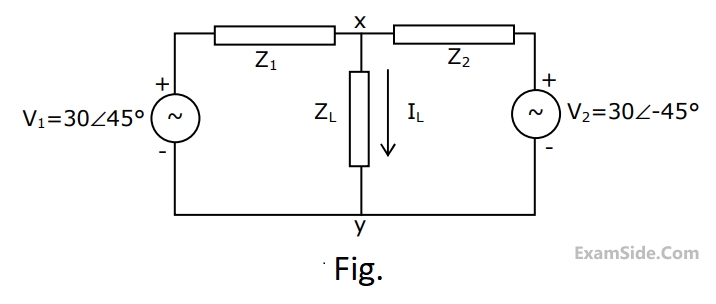

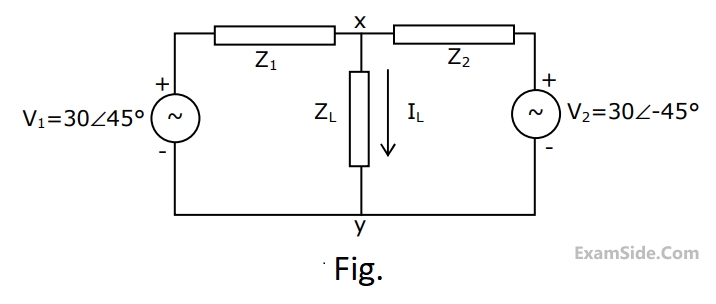

An electrical network is fed by two $$ac$$ sources, as shown in Fig. Given that

$${Z_1} = \left( {1 - j} \right)\Omega ,\,\,{Z_2} = \left( {1 + j} \right)\Omega $$ and $${Z_L} = \left( {1 + j0} \right)\Omega .$$ Obtain the Thevenin equivalent circuit (Thevenin voltage and impedance) across terminals $$X$$ and $$Y$$, and determine the current $${{\rm I}_L}$$ through the load $${Z_L}.$$

$${Z_1} = \left( {1 - j} \right)\Omega ,\,\,{Z_2} = \left( {1 + j} \right)\Omega $$ and $${Z_L} = \left( {1 + j0} \right)\Omega .$$ Obtain the Thevenin equivalent circuit (Thevenin voltage and impedance) across terminals $$X$$ and $$Y$$, and determine the current $${{\rm I}_L}$$ through the load $${Z_L}.$$

3

GATE EE 2002

MCQ (Single Correct Answer)

+1

-0.3

The graph of an electrical network has $$N$$ nodes and $$B$$ branches. The number of links, $$L$$, with respect to the choice of a tree, is given by

4

GATE EE 2002

Subjective

+5

-0

In the resistor network shown in Fig. all resistor values are $$1\,\,\Omega .$$ $$A$$ current of $$1A$$ passes from terminal $$a$$ to terminal $$b,$$ as shown in the figure. Calculate the voltage between terminals $$a$$ and $$b.$$ [Hint: You may exploit the symmetry of the circuit].

Paper analysis

Total Questions

Analog Electronics

7

Control Systems

7

Digital Electronics

5

Electric Circuits

11

Electrical and Electronics Measurement

3

Electrical Machines

10

Electromagnetic Fields

2

Engineering Mathematics

3

Power Electronics

7

Power System Analysis

10

Signals and Systems

5

More papers of GATE EE

GATE EE 2025

GATE EE 2024

GATE EE 2023

GATE EE 2022

GATE EE 2021

GATE EE 2020

GATE EE 2019

GATE EE 2018

GATE EE 2017 Set 1

GATE EE 2017 Set 2

GATE EE 2016 Set 2

GATE EE 2016 Set 1

GATE EE 2015 Set 1

GATE EE 2015 Set 2

GATE EE 2014 Set 3

GATE EE 2014 Set 2

GATE EE 2014 Set 1

GATE EE 2013

GATE EE 2012

GATE EE 2011

GATE EE 2010

GATE EE 2009

GATE EE 2008

GATE EE 2007

GATE EE 2006

GATE EE 2005

GATE EE 2004

GATE EE 2003

GATE EE 2002

GATE EE 2001

GATE EE 2000

GATE EE 1999

GATE EE 1998

GATE EE 1997

GATE EE 1996

GATE EE 1995

GATE EE 1994

GATE EE 1993

GATE EE 1992

GATE EE 1991

GATE EE

Papers

2025

2024

2023

2022

2021

2020

2019

2018

2013

2012

2011

2010

2009

2008

2007

2006

2005

2004

2003

2002

2001

2000

1999

1998

1997

1996

1995

1994

1993

1992

1991