1

GATE EE 2006

MCQ (Single Correct Answer)

+2

-0.6

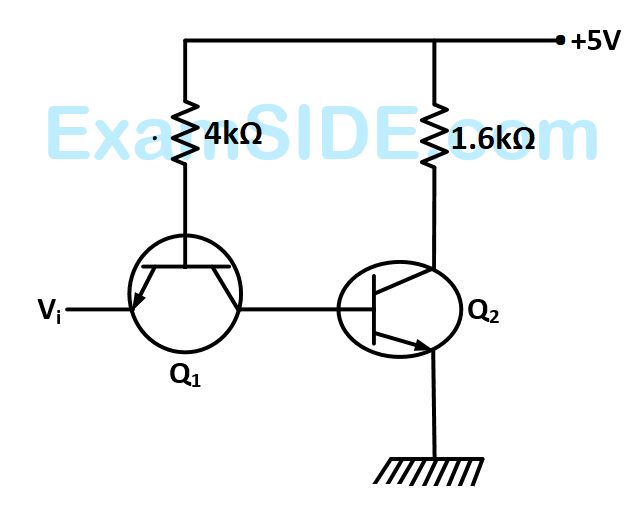

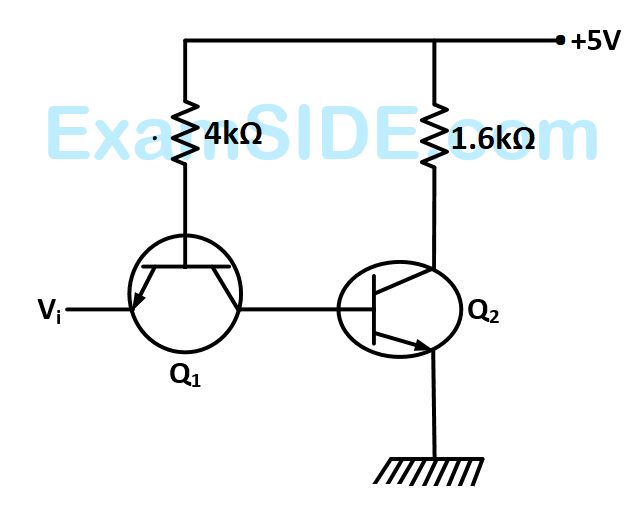

A TTL NOT gate circuit is shown in figure. Assuming $${V_{BE}} = 0.7\,v$$ of both the transistors, if $${V_i} = 3.0\,V,$$ then the states of the two transistors will be

2

GATE EE 2006

MCQ (Single Correct Answer)

+2

-0.6

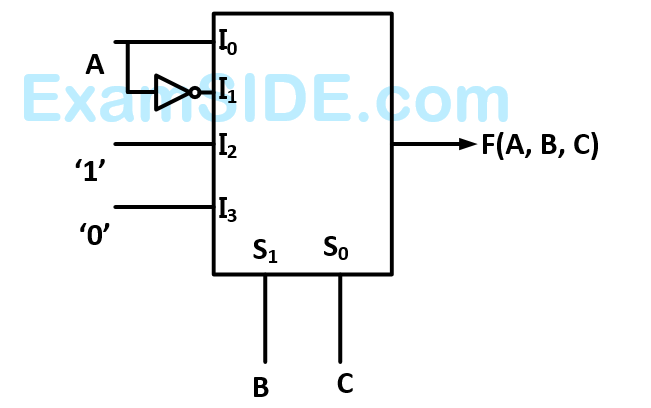

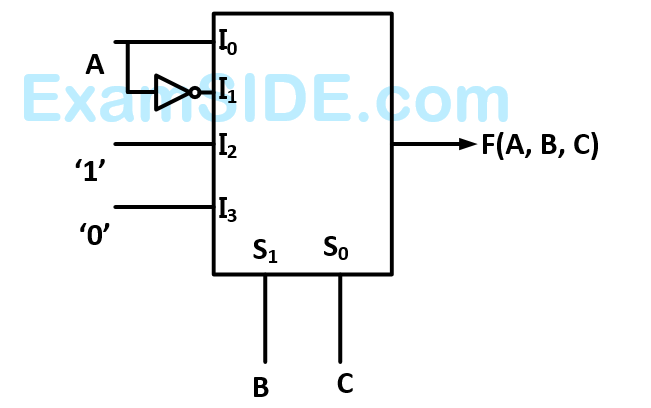

A $$4 \times 1\,\,MUX$$ is used to implement a $$3$$- input Boolean function as shown in figure. The Boolean function $$F\left( {A,\,\,B,\,\,C} \right)$$ implemented is

3

GATE EE 2006

MCQ (Single Correct Answer)

+1

-0.3

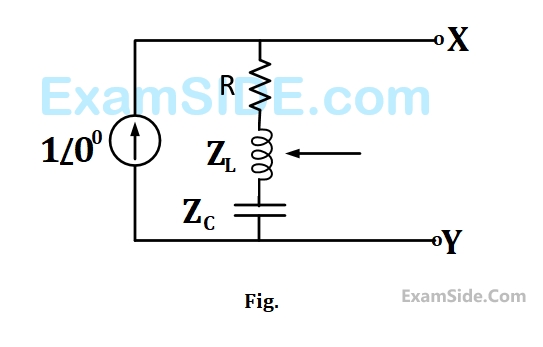

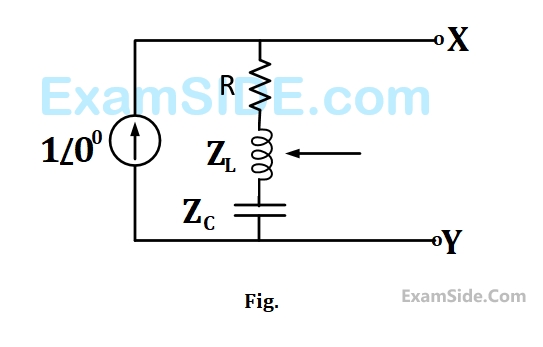

In the figure the current source is $$1\,\,\angle \,0\,A,$$ $$R = \,1\,\,\Omega ,$$ the impedances are $${Z_C} = - j\,\,\Omega ,$$ and $${Z_L} = 2\,j\,\,\Omega .$$ The Thevenin equivalent looking into the circuit across $$X-Y$$ is.

4

GATE EE 2006

MCQ (Single Correct Answer)

+2

-0.6

The parameters of the circuit shown in the figure are

$${R_i} = 1\,\,M\,\Omega ,\,\,{R_0} = 10\,\Omega ,\,\,A = {10^6}\,\,V/V.$$ If $${V_i} = 1\,\,\mu V,\,\,$$ the output voltage, input impedance and output impedance respectively are

$${R_i} = 1\,\,M\,\Omega ,\,\,{R_0} = 10\,\Omega ,\,\,A = {10^6}\,\,V/V.$$ If $${V_i} = 1\,\,\mu V,\,\,$$ the output voltage, input impedance and output impedance respectively are

Paper analysis

Total Questions

Analog Electronics

5

Control Systems

5

Digital Electronics

4

Electric Circuits

5

Electrical and Electronics Measurement

7

Electrical Machines

13

Electromagnetic Fields

3

Engineering Mathematics

1

Power Electronics

8

Power System Analysis

13

Signals and Systems

6

More papers of GATE EE

GATE EE 2025

GATE EE 2024

GATE EE 2023

GATE EE 2022

GATE EE 2021

GATE EE 2020

GATE EE 2019

GATE EE 2018

GATE EE 2017 Set 1

GATE EE 2017 Set 2

GATE EE 2016 Set 2

GATE EE 2016 Set 1

GATE EE 2015 Set 1

GATE EE 2015 Set 2

GATE EE 2014 Set 3

GATE EE 2014 Set 2

GATE EE 2014 Set 1

GATE EE 2013

GATE EE 2012

GATE EE 2011

GATE EE 2010

GATE EE 2009

GATE EE 2008

GATE EE 2007

GATE EE 2006

GATE EE 2005

GATE EE 2004

GATE EE 2003

GATE EE 2002

GATE EE 2001

GATE EE 2000

GATE EE 1999

GATE EE 1998

GATE EE 1997

GATE EE 1996

GATE EE 1995

GATE EE 1994

GATE EE 1993

GATE EE 1992

GATE EE 1991

GATE EE

Papers

2025

2024

2023

2022

2021

2020

2019

2018

2013

2012

2011

2010

2009

2008

2007

2006

2005

2004

2003

2002

2001

2000

1999

1998

1997

1996

1995

1994

1993

1992

1991