1

GATE CSE 2006

MCQ (Single Correct Answer)

+2

-0.6

Consider the relation enrolled (student, course) in which (student, course ) is the primary key, and the relation Paid (student, amount) where student is the primary key. Assume no null values and no foreign keys or integrity constraints. Assume that amounts $$6000, 7000, 8000,9000$$ and $$10000$$ were each paid by $$20$$% of the students. Consider these query plans (Plan $$1$$ on left, Plan $$2$$ on right) to ''List all courses taken by students who have paid more than $$x''$$.

A disk seek takes $$4ms$$, disk data transfer bandwidth is $$300MB/s$$ and checking a tuple to see if amount is greater than $$x$$ takes $$10\mu s.$$ Which of the following statements is correct?

2

GATE CSE 2006

MCQ (Single Correct Answer)

+2

-0.6

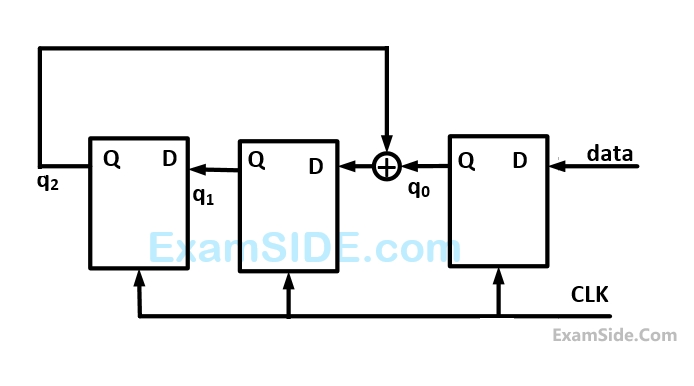

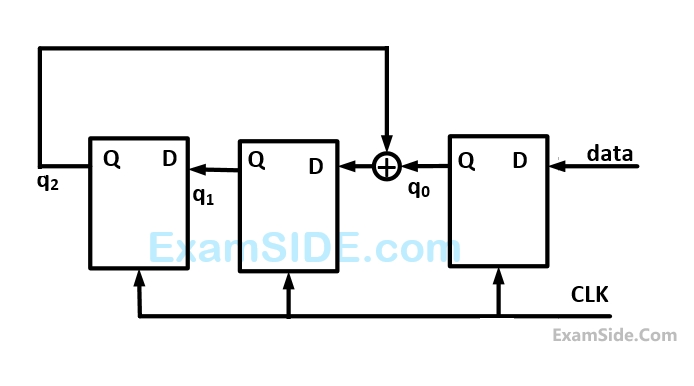

Consider the circuit in the diagram. The $$ \oplus $$ operator represents $$EX$$-$$OR.$$ The $$D$$ flip-flops are initialized to zeros (cleared).

The following data: $$100110000$$ is supplied to the ''data'' terminal in nine clock cycles. After that the values of $${q_2}{q_1}{q_0}$$ are

3

GATE CSE 2006

MCQ (Single Correct Answer)

+1

-0.3

You are given a free running clock with a duty cycle of $$50$$% and a digital waveform $$f$$ which changes only at the negative edge of the clock. Which one of the following circuits (using clocked $$D$$ flip-flops) will delay the phase of $$f$$ by $${180^0}?$$

4

GATE CSE 2006

MCQ (Single Correct Answer)

+2

-0.6

Consider the circuit above. Which one of the following options correctly represents $$f(x,y,z)?$$

Paper analysis

Total Questions

Algorithms

14

Compiler Design

6

Computer Networks

6

Computer Organization

9

Data Structures

12

Database Management System

8

Digital Logic

4

Discrete Mathematics

25

Operating Systems

8

Programming Languages

1

Theory of Computation

6

More papers of GATE CSE

GATE CSE 2025 Set 2

GATE CSE 2025 Set 1

GATE CSE 2024 Set 2

GATE CSE 2024 Set 1

GATE CSE 2023

GATE CSE 2022

GATE CSE 2021 Set 2

GATE CSE 2021 Set 1

GATE CSE 2020

GATE CSE 2019

GATE CSE 2018

GATE CSE 2017 Set 1

GATE CSE 2017 Set 2

GATE CSE 2016 Set 1

GATE CSE 2016 Set 2

GATE CSE 2015 Set 3

GATE CSE 2015 Set 1

GATE CSE 2015 Set 2

GATE CSE 2014 Set 3

GATE CSE 2014 Set 1

GATE CSE 2014 Set 2

GATE CSE 2013

GATE CSE 2012

GATE CSE 2011

GATE CSE 2010

GATE CSE 2009

GATE CSE 2008

GATE CSE 2007

GATE CSE 2006

GATE CSE 2005

GATE CSE 2004

GATE CSE 2003

GATE CSE 2002

GATE CSE 2001

GATE CSE 2000

GATE CSE 1999

GATE CSE 1998

GATE CSE 1997

GATE CSE 1996

GATE CSE 1995

GATE CSE 1994

GATE CSE 1993

GATE CSE 1992

GATE CSE 1991

GATE CSE 1990

GATE CSE 1989

GATE CSE 1988

GATE CSE 1987

GATE CSE

Papers

2023

2022

2020

2019

2018

2013

2012

2011

2010

2009

2008

2007

2006

2005

2004

2003

2002

2001

2000

1999

1998

1997

1996

1995

1994

1993

1992

1991

1990

1989

1988

1987