1

GATE CSE 2004

MCQ (Single Correct Answer)

+2

-0.6

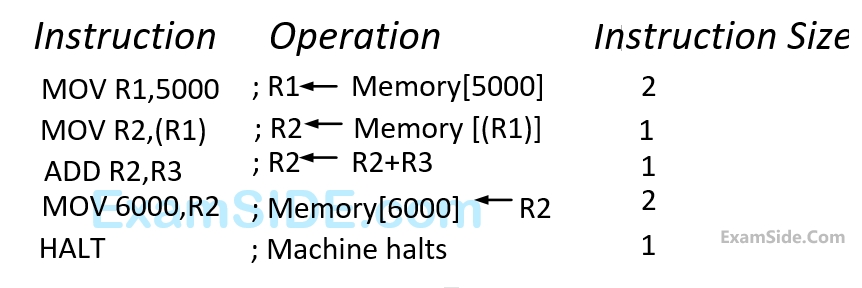

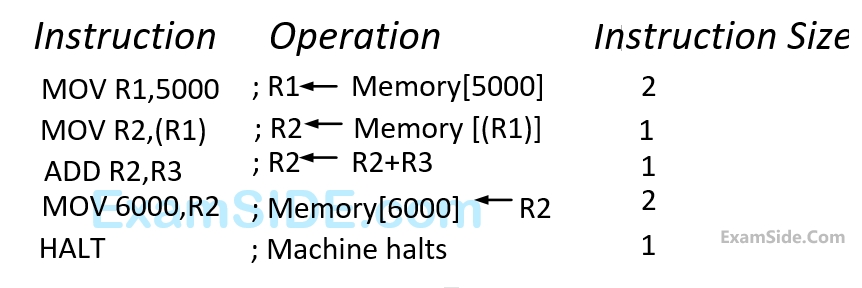

Consider the following program segment for a hypothetical $$CPU$$ having three user registers $$R1,R2, $$ and $$R3.$$

Consider that the memory is byte addressable with word size $$32$$ bits, and the program has been loaded starting from memory location $$1000$$ (decimal). If an interrupt occurs while the $$CPU$$ has been halted after executing the HALT instruction, the return address (in decimal) saved in the stack will be

2

GATE CSE 2004

MCQ (Single Correct Answer)

+1

-0.3

Which of the following addressing modes are suitable for program relocation at run time?

$$1.$$ Absolute addressing

$$2.$$ Based addressing

$$3.$$ Relative addressing

$$4.$$ Indirect addressing

$$1.$$ Absolute addressing

$$2.$$ Based addressing

$$3.$$ Relative addressing

$$4.$$ Indirect addressing

3

GATE CSE 2004

MCQ (Single Correct Answer)

+2

-0.6

A $$4$$-stage pipeline has the stage delays as $$150, 120,160$$ and $$140$$ nano seconds respectively. Registers that are used between the stages have a delay of $$5$$ nanoseconds each. Assuming constant clocking rate, the total time taken to process $$1000$$ data items on this pipeline will be

4

GATE CSE 2004

MCQ (Single Correct Answer)

+2

-0.6

Consider a small two-way set-associative cache memory, consisting of four blocks. For choosing the block to be replaced, uses the least recently used $$(LRU)$$ scheme. The number of cache misses for the following sequence of blocks addresses is $$8,12,0,12,8$$

Paper analysis

Total Questions

Algorithms

9

Compiler Design

3

Computer Networks

9

Computer Organization

11

Data Structures

14

Database Management System

13

Digital Logic

8

Discrete Mathematics

30

Operating Systems

7

Programming Languages

6

Theory of Computation

5

More papers of GATE CSE

GATE CSE 2025 Set 2

GATE CSE 2025 Set 1

GATE CSE 2024 Set 2

GATE CSE 2024 Set 1

GATE CSE 2023

GATE CSE 2022

GATE CSE 2021 Set 2

GATE CSE 2021 Set 1

GATE CSE 2020

GATE CSE 2019

GATE CSE 2018

GATE CSE 2017 Set 1

GATE CSE 2017 Set 2

GATE CSE 2016 Set 1

GATE CSE 2016 Set 2

GATE CSE 2015 Set 3

GATE CSE 2015 Set 1

GATE CSE 2015 Set 2

GATE CSE 2014 Set 3

GATE CSE 2014 Set 1

GATE CSE 2014 Set 2

GATE CSE 2013

GATE CSE 2012

GATE CSE 2011

GATE CSE 2010

GATE CSE 2009

GATE CSE 2008

GATE CSE 2007

GATE CSE 2006

GATE CSE 2005

GATE CSE 2004

GATE CSE 2003

GATE CSE 2002

GATE CSE 2001

GATE CSE 2000

GATE CSE 1999

GATE CSE 1998

GATE CSE 1997

GATE CSE 1996

GATE CSE 1995

GATE CSE 1994

GATE CSE 1993

GATE CSE 1992

GATE CSE 1991

GATE CSE 1990

GATE CSE 1989

GATE CSE 1988

GATE CSE 1987

GATE CSE

Papers

2023

2022

2020

2019

2018

2013

2012

2011

2010

2009

2008

2007

2006

2005

2004

2003

2002

2001

2000

1999

1998

1997

1996

1995

1994

1993

1992

1991

1990

1989

1988

1987