In the given circuit, the diodes are ideal. The current I through the diode D1 in milliamperes is _____ (rounded off to two decimal places).

A difference amplifier is shown in the figure. Assume the op-amp to be ideal. The CMRR (in dB) of the difference amplifier is ________ (rounded off to 2 decimal places).

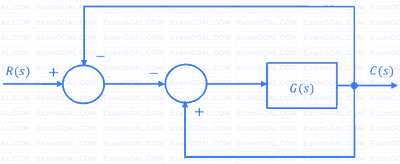

For the block-diagram shown in the figure, the transfer function $\frac{C(s)}{R(s)}$ is

Consider the standard second-order system of the form $\frac{\omega_n^2}{s^2 + 2\zeta\omega_n s + \omega_n^2}$ with the poles $p$ and $p^\ast$ having negative real parts. The pole locations are also shown in the figure. Now consider two such second-order systems as defined below:

System 1: $\omega_n = 3$ rad/sec and $\theta = 60^{\circ}$

System 2: $\omega_n = 1$ rad/sec and $\theta = 70^{\circ}$

Which one of the following statements is correct?