1

GATE EE 2017 Set 2

Numerical

+2

-0

Consider the system described by the following state space representation

$$\eqalign{ & \left[ {\matrix{ {\mathop {{x_1}}\limits^ \bullet \left( t \right)} \cr {\mathop {{x_2}}\limits^ \bullet \left( t \right)} \cr } } \right] = \left[ {\matrix{ 0 & 1 \cr 0 & { - 2} \cr } } \right]\left[ {\matrix{ {{x_1}\left( t \right)} \cr {{x_2}\left( t \right)} \cr } } \right] + \left[ {\matrix{ 0 \cr 1 \cr } } \right]u\left( t \right) \cr & y\left( t \right) = \left[ {\matrix{ 1 & 0 \cr } } \right]\left[ {\matrix{ {{x_1}\left( t \right)} \cr {{x_2}\left( t \right)} \cr } } \right] \cr} $$

$$\eqalign{ & \left[ {\matrix{ {\mathop {{x_1}}\limits^ \bullet \left( t \right)} \cr {\mathop {{x_2}}\limits^ \bullet \left( t \right)} \cr } } \right] = \left[ {\matrix{ 0 & 1 \cr 0 & { - 2} \cr } } \right]\left[ {\matrix{ {{x_1}\left( t \right)} \cr {{x_2}\left( t \right)} \cr } } \right] + \left[ {\matrix{ 0 \cr 1 \cr } } \right]u\left( t \right) \cr & y\left( t \right) = \left[ {\matrix{ 1 & 0 \cr } } \right]\left[ {\matrix{ {{x_1}\left( t \right)} \cr {{x_2}\left( t \right)} \cr } } \right] \cr} $$

If $$u(t)$$ is a unit step input and $$\left[ {\matrix{ {{x_1}\left( 0 \right)} \cr {{x_2}\left( 0 \right)} \cr } } \right] = \left[ {\matrix{ 1 \cr 0 \cr } } \right],$$ the value of output $$y(t)$$ at $$t=1$$ sec (rounded off to three decimal places) is _____________.

Your input ____

2

GATE EE 2017 Set 2

MCQ (Single Correct Answer)

+1

-0.3

For a $$3$$ -input logic circuit shown below, the output $$Z$$ can be expressed as

3

GATE EE 2017 Set 2

Numerical

+2

-0

For the synchronous sequential circuit shown below, the output $$Z$$ is zero for the initial conditions $${Q_A}{Q_B}{Q_C} = Q{'_A}Q{'_B}Q{'_C} = 100.$$

The minimum number if clock cycles after which the output $$Z$$ would again become zero is _____________.

Your input ____

4

GATE EE 2017 Set 2

Numerical

+1

-0

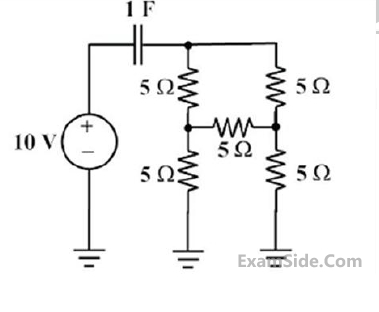

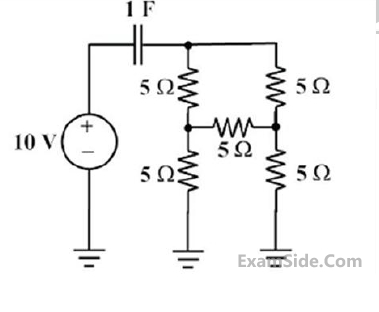

The initial charge in the 1 F capacitor present in the circuit shown is zero. The energy in joules

transferred from the DC source until steady state condition is reached equals ______. (Give the

answer up to one decimal place.)

Your input ____

Paper analysis

Total Questions

Analog Electronics

2

Control Systems

5

Digital Electronics

2

Electric Circuits

6

Electrical and Electronics Measurement

3

Electrical Machines

9

Electromagnetic Fields

3

Engineering Mathematics

9

Power Electronics

6

Power System Analysis

6

Signals and Systems

3

More papers of GATE EE

GATE EE 2025

GATE EE 2024

GATE EE 2023

GATE EE 2022

GATE EE 2021

GATE EE 2020

GATE EE 2019

GATE EE 2018

GATE EE 2017 Set 2

GATE EE 2017 Set 1

GATE EE 2016 Set 2

GATE EE 2016 Set 1

GATE EE 2015 Set 1

GATE EE 2015 Set 2

GATE EE 2014 Set 2

GATE EE 2014 Set 3

GATE EE 2014 Set 1

GATE EE 2013

GATE EE 2012

GATE EE 2011

GATE EE 2010

GATE EE 2009

GATE EE 2008

GATE EE 2007

GATE EE 2006

GATE EE 2005

GATE EE 2004

GATE EE 2003

GATE EE 2002

GATE EE 2001

GATE EE 2000

GATE EE 1999

GATE EE 1998

GATE EE 1997

GATE EE 1996

GATE EE 1995

GATE EE 1994

GATE EE 1993

GATE EE 1992

GATE EE 1991

GATE EE

Papers

2025

2024

2023

2022

2021

2020

2019

2018

2013

2012

2011

2010

2009

2008

2007

2006

2005

2004

2003

2002

2001

2000

1999

1998

1997

1996

1995

1994

1993

1992

1991