1

GATE CSE 2003

MCQ (Single Correct Answer)

+5

-1.5

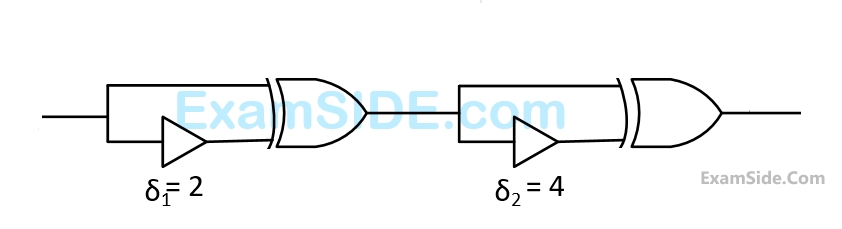

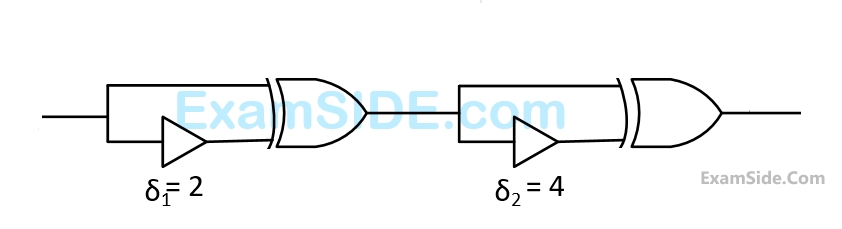

Consider the following circuit composed of $$XOR$$ gates are non-inverting buffers.

The non-inverting buffers have delays $${\delta _1} = 2$$ $$ns$$ and $${\delta _2} = 4$$ $$ns$$ as shown in the figure. Both $$XOR$$ gates and all wires have zero delay. Assume that all gate inputs, outputs and wires are stable at logic level $$0$$ at time$$0.$$ If the following waveform is applied at input $$A$$, how many transition(s) (change of logic levels) occurs(s) at $$B$$ during the interval from $$0$$ to $$10$$ $$ns?$$

2

GATE CSE 2003

MCQ (Single Correct Answer)

+1

-0.3

$$A$$ system of equations represented by $$AX=0$$ where $$X$$ is a column vector of unknown and $$A$$ is a square matrix containing coefficients has a non-trival solution when $$A$$ is.

3

GATE CSE 2003

MCQ (Single Correct Answer)

+1

-0.3

$$\mathop {Lim}\limits_{x \to 0} \,{{Si{n^2}x} \over x} = \_\_\_\_.$$

4

GATE CSE 2003

MCQ (Single Correct Answer)

+2

-0.6

How many perfect matchings are there in a complete graph of 6 vertices?

Paper analysis

Total Questions

Algorithms

9

Compiler Design

9

Computer Networks

5

Computer Organization

2

Data Structures

4

Database Management System

5

Digital Logic

5

Discrete Mathematics

11

Operating Systems

8

Programming Languages

7

Theory of Computation

8

More papers of GATE CSE

GATE CSE 2025 Set 2

GATE CSE 2025 Set 1

GATE CSE 2024 Set 2

GATE CSE 2024 Set 1

GATE CSE 2023

GATE CSE 2022

GATE CSE 2021 Set 2

GATE CSE 2021 Set 1

GATE CSE 2020

GATE CSE 2019

GATE CSE 2018

GATE CSE 2017 Set 2

GATE CSE 2017 Set 1

GATE CSE 2016 Set 2

GATE CSE 2016 Set 1

GATE CSE 2015 Set 3

GATE CSE 2015 Set 2

GATE CSE 2015 Set 1

GATE CSE 2014 Set 3

GATE CSE 2014 Set 2

GATE CSE 2014 Set 1

GATE CSE 2013

GATE CSE 2012

GATE CSE 2011

GATE CSE 2010

GATE CSE 2009

GATE CSE 2008

GATE CSE 2007

GATE CSE 2006

GATE CSE 2005

GATE CSE 2004

GATE CSE 2003

GATE CSE 2002

GATE CSE 2001

GATE CSE 2000

GATE CSE 1999

GATE CSE 1998

GATE CSE 1997

GATE CSE 1996

GATE CSE 1995

GATE CSE 1994

GATE CSE 1993

GATE CSE 1992

GATE CSE 1991

GATE CSE 1990

GATE CSE 1989

GATE CSE 1988

GATE CSE 1987

GATE CSE

Papers

2023

2022

2020

2019

2018

2013

2012

2011

2010

2009

2008

2007

2006

2005

2004

2003

2002

2001

2000

1999

1998

1997

1996

1995

1994

1993

1992

1991

1990

1989

1988

1987