Sequential Circuits · Digital Electronics · GATE EE

Marks 1

In the circuit, the present value of $Z$ is $1$. Neglecting the delay in the combinatorial circuit, the values of $S$ and $Z$, respectively, after the application of the clock will be

A MOD-2 and a MOD-5 up-counter when cascaded together results in a MOD _________ counter. (in integer).

The maximum clock frequency in MHz of a 4-stage ripple counter, utilizing flip-flops, with each flip-flop having a propagation delay of 20 ns, is ________. (round off to one decimal place).

The logic gate represented by the state diagram is

Marks 2

The minimum number if clock cycles after which the output $$Z$$ would again become zero is _____________.

It the state $${Q_A}{Q_B}$$ of the counter at the clock time $${t_n}$$ is $$'10'$$ then the state $${Q_A}{Q_B}$$ of the counter at $${t_n} + 3$$ (after three clock cycles) will be

Marks 5

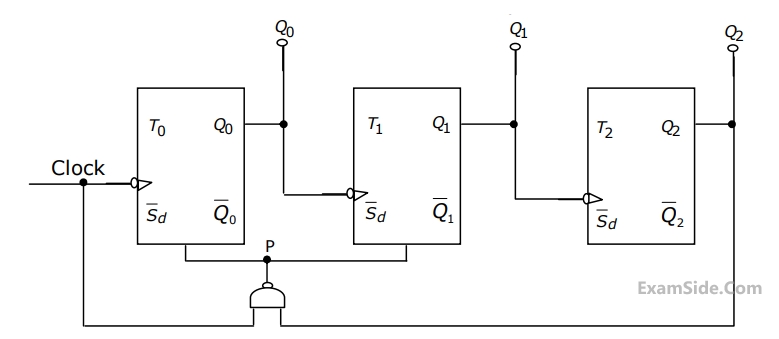

$$(a)$$ Create a table of $${Q_0},{Q_1},{Q_2}$$ and $$A$$ in the format given below for $$10$$ successive

$$\,\,\,\,\,\,\,\,$$ input cycles of the clock $$CLK1.$$

$$(b)$$ Determine the module number of the counter.

$$(c)$$ Modify the circuit of Fig. to create a modulo$$-6$$ counter using the same

$$\,\,\,\,\,\,\,$$ components used in the figure.

$$(b)$$ Sketch the output waveforms at $${Q_1},{Q_2}$$ and $${Q_3}$$.

$$(c)$$ What function does this circuit perform.