1

GATE CSE 2016 Set 1

Numerical

+1

-0

A processor can support a maximum memory of $$4$$ $$GB,$$ where the memory is word-addressable (a word consists of two bytes). The size of the address bus of the processor is at least ___________ bits.

Your input ____

2

GATE CSE 2016 Set 1

Numerical

+1

-0

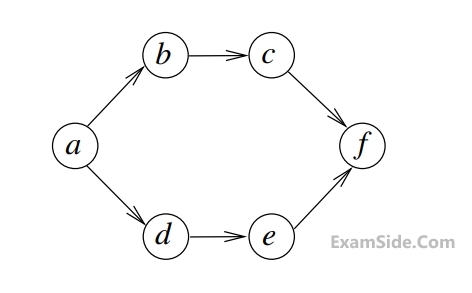

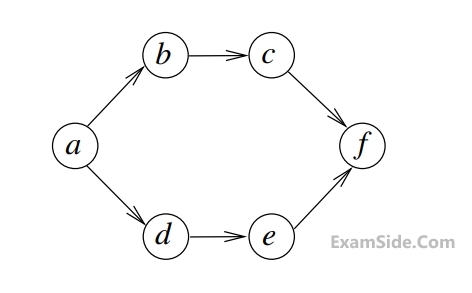

Consider the following directed graph:

The number of different topological orderings of the vertices of the graph is ________________.

Your input ____

3

GATE CSE 2016 Set 1

MCQ (Single Correct Answer)

+1

-0.3

A queue is implemented using an array such that ENQUEUE and DEQUEUE operations are performed efficiently. Which one of the following statements is CORRECT ($$n$$ refers to the number of items in the queue)?

4

GATE CSE 2016 Set 1

MCQ (Single Correct Answer)

+1

-0.3

Which of the following is NOT a superkey in a relational schema with attributes $$V, W, X, Y, Z$$ and primary key $$V Y?$$

Paper analysis

Total Questions

Algorithms

5

Compiler Design

3

Computer Networks

6

Computer Organization

3

Data Structures

2

Database Management System

4

Digital Logic

5

Discrete Mathematics

9

Operating Systems

4

Programming Languages

2

Theory of Computation

6

General Aptitude

10

More papers of GATE CSE

GATE CSE 2025 Set 2

GATE CSE 2025 Set 1

GATE CSE 2024 Set 2

GATE CSE 2024 Set 1

GATE CSE 2023

GATE CSE 2022

GATE CSE 2021 Set 2

GATE CSE 2021 Set 1

GATE CSE 2020

GATE CSE 2019

GATE CSE 2018

GATE CSE 2017 Set 1

GATE CSE 2017 Set 2

GATE CSE 2016 Set 1

GATE CSE 2016 Set 2

GATE CSE 2015 Set 3

GATE CSE 2015 Set 1

GATE CSE 2015 Set 2

GATE CSE 2014 Set 3

GATE CSE 2014 Set 1

GATE CSE 2014 Set 2

GATE CSE 2013

GATE CSE 2012

GATE CSE 2011

GATE CSE 2010

GATE CSE 2009

GATE CSE 2008

GATE CSE 2007

GATE CSE 2006

GATE CSE 2005

GATE CSE 2004

GATE CSE 2003

GATE CSE 2002

GATE CSE 2001

GATE CSE 2000

GATE CSE 1999

GATE CSE 1998

GATE CSE 1997

GATE CSE 1996

GATE CSE 1995

GATE CSE 1994

GATE CSE 1993

GATE CSE 1992

GATE CSE 1991

GATE CSE 1990

GATE CSE 1989

GATE CSE 1988

GATE CSE 1987

GATE CSE

Papers

2023

2022

2020

2019

2018

2013

2012

2011

2010

2009

2008

2007

2006

2005

2004

2003

2002

2001

2000

1999

1998

1997

1996

1995

1994

1993

1992

1991

1990

1989

1988

1987