1

GATE CSE 2019

MCQ (Single Correct Answer)

+1

-0.33

A certain processor uses a fully associative cache of size 16 kB. The cache block size is 16 bytes. Assume that the main memory is byte addressable and uses a 32-bit address. How many bits are required for the Tag and the Index fields resectively in the addresses generated by the processor?

2

GATE CSE 2019

Numerical

+2

-0

A certain processor deploys a single-level cache. The cache block size is 8 words and the word size is 4 bytes. The memory system uses a $60-\mathrm{MHz}$ clock. To service a cache miss, the memory controller first takes 1 cycle to accept the starting address of the block, it then takes 3 cycles to fetch all the eight words of the block, and finally transmits the words of the requested block at the rate of 1 word per cycle. The maximum bandwidth for the memory system when the program running on the processor issues a series of read operations is

_________ $\times 10^6$ bytes $/ \mathrm{sec}$.

Your input ____

3

GATE CSE 2019

Numerical

+2

-0

Let T be a full binary tree with 8 leaves. (A full binary tree has every level full). Suppose two leaves a and b of T are chosen uniformly and independently at random. The expected value of the distance between a and b in T (i.e., the number of edges in the unique path between a and b) is (rounded off to 2 decimal places) _____.

Your input ____

4

GATE CSE 2019

Numerical

+2

-0

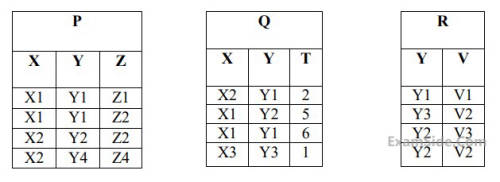

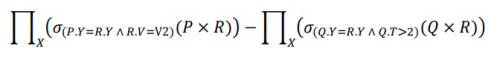

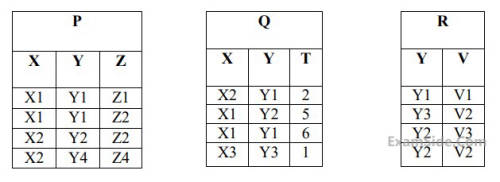

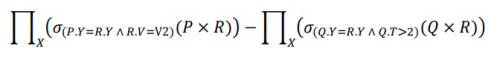

Consider the following relations P(X,Y,Z), Q(X,Y,T) and R(Y,V).

How many tuples will be returned by the following relational algebra query?

How many tuples will be returned by the following relational algebra query?

Your input ____

Paper analysis

Total Questions

Algorithms

4

Compiler Design

4

Computer Networks

6

Computer Organization

3

Data Structures

1

Database Management System

5

Digital Logic

5

Discrete Mathematics

10

Operating Systems

6

Programming Languages

6

Theory of Computation

5

General Aptitude

10

More papers of GATE CSE

GATE CSE 2025 Set 2

GATE CSE 2025 Set 1

GATE CSE 2024 Set 2

GATE CSE 2024 Set 1

GATE CSE 2023

GATE CSE 2022

GATE CSE 2021 Set 2

GATE CSE 2021 Set 1

GATE CSE 2020

GATE CSE 2019

GATE CSE 2018

GATE CSE 2017 Set 1

GATE CSE 2017 Set 2

GATE CSE 2016 Set 1

GATE CSE 2016 Set 2

GATE CSE 2015 Set 3

GATE CSE 2015 Set 1

GATE CSE 2015 Set 2

GATE CSE 2014 Set 3

GATE CSE 2014 Set 1

GATE CSE 2014 Set 2

GATE CSE 2013

GATE CSE 2012

GATE CSE 2011

GATE CSE 2010

GATE CSE 2009

GATE CSE 2008

GATE CSE 2007

GATE CSE 2006

GATE CSE 2005

GATE CSE 2004

GATE CSE 2003

GATE CSE 2002

GATE CSE 2001

GATE CSE 2000

GATE CSE 1999

GATE CSE 1998

GATE CSE 1997

GATE CSE 1996

GATE CSE 1995

GATE CSE 1994

GATE CSE 1993

GATE CSE 1992

GATE CSE 1991

GATE CSE 1990

GATE CSE 1989

GATE CSE 1988

GATE CSE 1987

GATE CSE

Papers

2023

2022

2020

2019

2018

2013

2012

2011

2010

2009

2008

2007

2006

2005

2004

2003

2002

2001

2000

1999

1998

1997

1996

1995

1994

1993

1992

1991

1990

1989

1988

1987