1

GATE CSE 2014 Set 2

MCQ (Single Correct Answer)

+2

-0.6

The value of a float type variable is represented using the single-precision $$32$$-bit floating point format of $$IEEE-754$$ standard that uses $$1$$ bit for sign, $$8$$ bits for biased exponent and $$23$$ bits for mantissa. $$A$$ float type variable $$X$$ is assigned the decimal value of $$−14.25.$$ The representation of $$X$$ in hexadecimal notation is

2

GATE CSE 2014 Set 2

Numerical

+2

-0

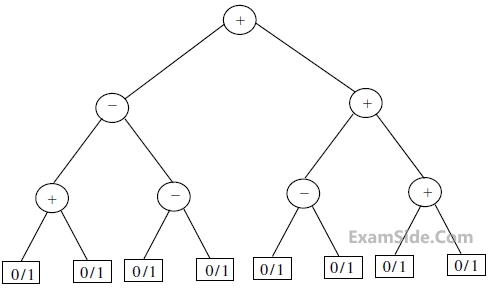

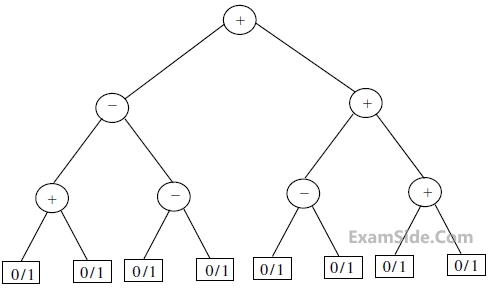

Consider the expression tree shown. Each leaf represents a numerical value, which can either be 0 or 1. Over all possible choices of the values at the leaves, the maximum possible value of the expression represented by the tree is ___.

Your input ____

3

GATE CSE 2014 Set 2

MCQ (Single Correct Answer)

+1

-0.3

Consider the tree arcs of a BFS traversal from a source node W in an unweighted, connected,

undirected graph. The tree T formed by the tree arcs is a data structure for computing

4

GATE CSE 2014 Set 2

MCQ (Single Correct Answer)

+2

-0.6

Suppose a stack implementation supports an instruction REVERSE, which reverses the order of elements on the stack, in addition to the PUSH and POP instructions. Which one of the following statements is TRUE with respect to this modified stack?

Paper analysis

Total Questions

Algorithms

5

Compiler Design

2

Computer Networks

6

Computer Organization

5

Data Structures

3

Database Management System

5

Digital Logic

3

Discrete Mathematics

9

Operating Systems

4

Programming Languages

5

Software Engineering

1

Theory of Computation

5

More papers of GATE CSE

GATE CSE 2025 Set 2

GATE CSE 2025 Set 1

GATE CSE 2024 Set 2

GATE CSE 2024 Set 1

GATE CSE 2023

GATE CSE 2022

GATE CSE 2021 Set 2

GATE CSE 2021 Set 1

GATE CSE 2020

GATE CSE 2019

GATE CSE 2018

GATE CSE 2017 Set 1

GATE CSE 2017 Set 2

GATE CSE 2016 Set 1

GATE CSE 2016 Set 2

GATE CSE 2015 Set 3

GATE CSE 2015 Set 1

GATE CSE 2015 Set 2

GATE CSE 2014 Set 3

GATE CSE 2014 Set 1

GATE CSE 2014 Set 2

GATE CSE 2013

GATE CSE 2012

GATE CSE 2011

GATE CSE 2010

GATE CSE 2009

GATE CSE 2008

GATE CSE 2007

GATE CSE 2006

GATE CSE 2005

GATE CSE 2004

GATE CSE 2003

GATE CSE 2002

GATE CSE 2001

GATE CSE 2000

GATE CSE 1999

GATE CSE 1998

GATE CSE 1997

GATE CSE 1996

GATE CSE 1995

GATE CSE 1994

GATE CSE 1993

GATE CSE 1992

GATE CSE 1991

GATE CSE 1990

GATE CSE 1989

GATE CSE 1988

GATE CSE 1987

GATE CSE

Papers

2023

2022

2020

2019

2018

2013

2012

2011

2010

2009

2008

2007

2006

2005

2004

2003

2002

2001

2000

1999

1998

1997

1996

1995

1994

1993

1992

1991

1990

1989

1988

1987